# **T55 Data Sheet**

DST55-v2.4 April 2022 www.elitestek.com

# **Contents**

| Introduction                                               | 3   |

|------------------------------------------------------------|-----|

| Features                                                   | 3   |

| Available Package Options                                  | 4   |

| Device Core Functional Description                         | 5   |

| XLR Cell                                                   | 5   |

| Logic Cell                                                 | 6   |

| Embedded Memory                                            |     |

| Multipliers                                                |     |

| Global Clock Network                                       | 7   |

| Clock and Control Distribution Network                     |     |

| Global Clock Location                                      | 8   |

| Device Interface Functional Description                    | 10  |

| Interface Block Connectivity                               |     |

| General-Purpose I/O Logic and Buffer                       |     |

| Complex I/O Buffer                                         | 12  |

| Double-Data I/O                                            |     |

| I/O Banks                                                  |     |

| PLL                                                        |     |

| LVDS                                                       |     |

| LVDS TX                                                    |     |

| LVDS RX                                                    |     |

| MIPI                                                       |     |

| MIPI TXMIPI RX                                             |     |

| D-PHY Timing Parameters                                    |     |

| DDR DRAM                                                   |     |

| DDR Interface Designer Settings                            |     |

|                                                            |     |

| Power Up Sequence                                          |     |

| Power Supply Current Transient                             | 45  |

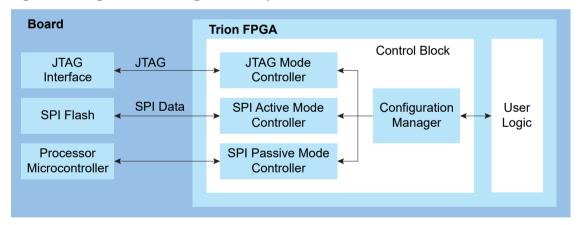

| Configuration                                              | 45  |

| Supported Configuration Modes                              |     |

| 9                                                          |     |

| DC and Switching Characteristics                           | 4/  |

| LVDS I/O Electrical and Timing Specifications              | 53  |

|                                                            |     |

| ESD Performance                                            | 53  |

| MIPI Electrical Specifications and Timing                  | 54  |

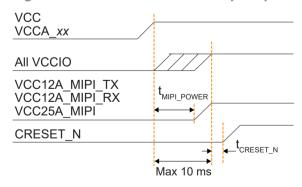

| MIPI Power-Up Timing                                       |     |

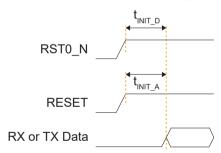

| MIPI Reset Timing                                          |     |

| DIL Timin and AC Characteristics                           | F-7 |

| PLL Timing and AC Characteristics                          | 57  |

| Configuration Timing                                       | 58  |

| Maximum t <sub>USFR</sub> for SPI Active and Passive Modes |     |

|                                                            |     |

| Pinout Description                                         | 61  |

| Efinity Software Support                                   | 65  |

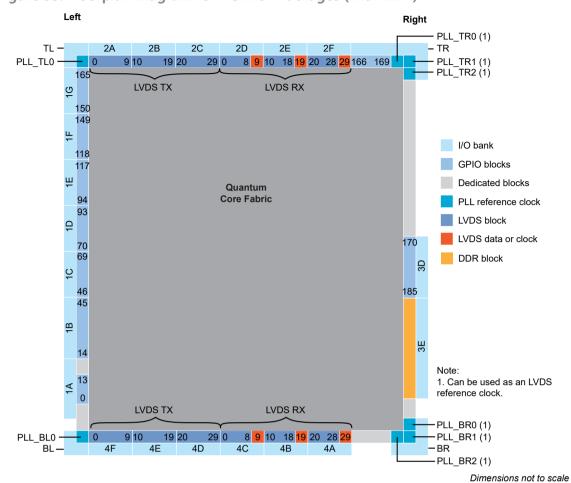

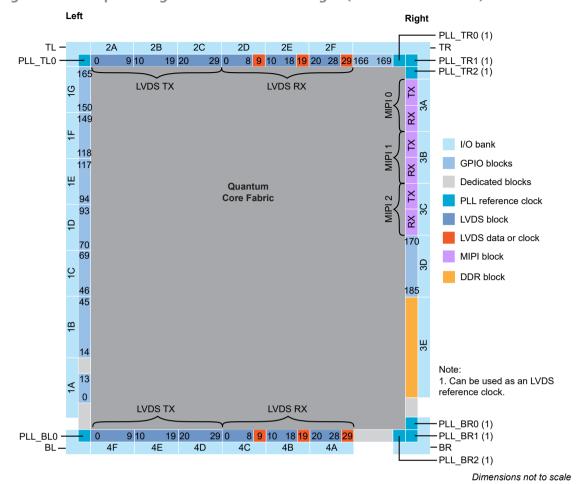

| T55 Interface Floorplan                                    | 65  |

| Ordering Codes                                             | 67  |

| Revision History                                           | 68  |

# Introduction

The T55 FPGA features the high-density, low-power 易灵思® Quantum™ architecture wrapped with an I/O interface for easy integration. With a high I/O to logic ratio and differential I/O support, T55 FPGAs supports a variety of applications that need wide I/O connectivity. The T55 also includes a MIPI D-PHY with a built-in, royalty-free CSI-2 controller, which is the most popular camera interface used in the mobile industry. Additionally, T55 FPGAs support a DDR3, LPDDR3, LPDDR2 PHY with memory controller hard IP that provides faster access to data stored in memory. The carefully tailored combination of core resources and I/O provides enhanced capability for applications such as embedded vision, voice and gesture recognition, intelligent sensor hubs, power management, and LED drivers.

### **Features**

- High-density, low-power Quantum<sup>™</sup> architecture

- Built on SMIC 40 nm process

- FPGA interface blocks

- GPIO

- PLL

- LVDS 800 Mbps per lane with up to 52 TX pairs and 52 RX pairs

- MIPI DPHY with CSI-2 controller hard IP, 1.5 Gbps per lane

- DDR3, DDR3L, LPDDR3, LPDDR2 x32 PHY (supporting x16 or x32 DQ widths) with memory controller hard IP, up to 1066 Mbps

- Programmable high-performance I/O

- Supports 1.8, 2.5, and 3.3 V single-ended I/O standards and interfaces

- Flexible on-chip clocking

- 16 low-skew global clock signals can be driven from off-chip external clock signals or PLL synthesized clock signals

- PLL support

- Flexible device configuration

- Standard SPI interface (active, passive, and daisy chain)

- JTAG interface

- Fully supported by the Efinity<sup>®</sup> software, an RTL-to-bitstream compiler

**Table 1: T55 FPGA Resources**

| LEs <sup>(1)</sup> | Global Clock<br>Networks | Global Control<br>Networks | Embedded<br>Memory (kbits) | Embedded<br>Memory<br>Blocks (5 Kbits) | Embedded<br>Multipliers |

|--------------------|--------------------------|----------------------------|----------------------------|----------------------------------------|-------------------------|

| 54,195             | Up to 16                 | Up to 16                   | 2,765                      | 540                                    | 150                     |

<sup>(1)</sup> Logic capacity in equivalent LE counts.

**Table 2: T55 Package-Dependent Resources**

| Resource                                               | BGA324                     | BGA484                         | BGA576                         |

|--------------------------------------------------------|----------------------------|--------------------------------|--------------------------------|

| Available GPIO <sup>(2)</sup>                          | 130                        | 256                            | 278                            |

| Global clocks from GPIO pins                           | 5                          | 16                             | 14                             |

| Global controls from GPIO pins                         | 5                          | 16                             | 14                             |

| PLLs                                                   | 7                          | 8                              | 8                              |

| LVDS                                                   | 20 TX pairs                | 40 TX pairs                    | 52 TX pairs                    |

|                                                        | 26 RX pairs                | 40 RX pairs                    | 52 RX pairs                    |

| MIPI DPHY with CSI-2 controller                        | 2 TX blocks                | _                              | 3 TX blocks                    |

| (4 data lanes, 1 clock lane)                           | 2 RX blocks                |                                | 3 RX blocks                    |

| DDR3, DDR3L, LPDDR3, LPDDR2 PHY with memory controller | 1 block (x16<br>DQ widths) | 1 block (x16 or x32 DQ widths) | 1 block (x16 or x32 DQ widths) |

Learn more: Refer to the Trion Packaging User Guide for the package outlines and markings.

# **Available Package Options**

**Table 3: Available Packages**

| Package       | Dimensions (mm x mm) | Pitch (mm) |

|---------------|----------------------|------------|

| 324-ball FBGA | 12 x 12              | 0.65       |

| 484-ball FBGA | 18 x 18              | 0.80       |

| 576-ball FBGA | 16 x 16              | 0.65       |

<sup>(2)</sup> The LVDS I/O pins are dual-purpose. The full number of GPIO are available when all LVDS I/O pins are in GPIO mode. GPIO and LVDS as GPIO supports different features. See **Table 9: Supported Features for GPIO and LVDS as GPIO** on page 12.

# **Device Core Functional Description**

T55 FPGAs feature an eXchangeable Logic and Routing (XLR) cell that 易灵思 has optimized for a variety of applications. Trion® FPGAs contain three building blocks constructed from XLR cells: logic elements, embedded memory blocks, and multipliers. Each FPGA in the Trion® family has a custom number of building blocks to fit specific application needs. As shown in the following figure, the FPGA includes I/O ports on all four sides, as well as columns of XLR cells, memory, and multipliers. A control block within the FPGA handles configuration.

Quantum Fabric

I/O Ports from Core to Device Interface

XLR Cells and Routing

Each Device Contains Unique Interface Blocks such as GPIO and PLL

Note: The number and locations of rows and columns are shown for illustration purposes only. The actual number and position depends on the core.

Device Interface

Figure 1: T55 FPGA Block Diagram

### XLR Cell

The eXchangeable Logic and Routing (XLR) cell is the basic building block of the Quantum™ architecture. The 易灵思 XLR cell combines logic and routing and supports both functions interchangeably. This unique innovation greatly enhances the transistor flexibility and utilization rate, thereby reducing transistor counts and silicon area significantly.

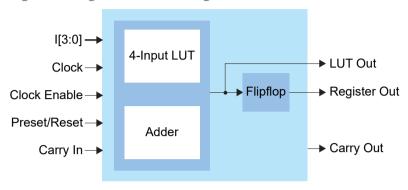

# Logic Cell

The logic cell comprises a 4-input LUT or a full adder plus a register (flipflop). You can program each LUT as any combinational logic function with four inputs. You can configure multiple logic cells to implement arithmetic functions such as adders, subtractors, and counters.

Figure 2: Logic Cell Block Diagram

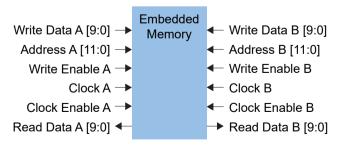

# **Embedded Memory**

The core has 5-kbit high-speed, synchronous, embedded SRAM memory blocks. Memory blocks can operate as single-port RAM, simple dual-port RAM, true dual-port RAM, FIFOs, or ROM. You can initialize the memory content during configuration. The Efinity® software includes a memory cascading feature to connect multiple blocks automatically to form a larger array. This feature enables you to instantiate deeper or wider memory modules.

Note: The block RAM content is random and undefined if it is not initialized.

The memory read and write ports have the following modes for addressing the memory (depth x width):

| 256 x 16 | 1024 x 4 | 4096 x 1 | 512 x 10 |

|----------|----------|----------|----------|

| 512 x 8  | 2048 x 2 | 256 x 20 | 1024 x 5 |

The read and write ports support independently configured data widths.

Figure 3: Embedded Memory Block Diagram (True Dual-Port Mode)

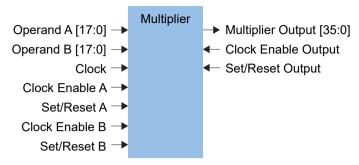

# **Multipliers**

The FPGA has high-performance multipliers that support 18 x 18 fixed-point multiplication. Each multiplier takes two signed 18-bit input operands and generates a signed 36-bit output product. The multiplier has optional registers on the input and output ports.

Figure 4: Multiplier Block Diagram

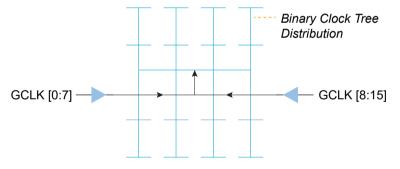

# Global Clock Network

The global clock networks are balanced clock trees that feed all FPGA modules. Each network has dedicated clock-enable logic to save power by disabling the clock tree at the root. The logic dynamically enables/disables the network and guarantees no glitches at the output.

**Figure 5: Global Clock Network**

#### Clock and Control Distribution Network

The global clock network is distributed through the device to provide clocking for the core's LEs, memory, multipliers, and I/O blocks. Designers can access the T55 global clock network using the global clock GPIO pins, PLL outputs, and core-generated clocks. Similarly, the T55 has GPIO pins (the number varies by package) that the designer can configure as control inputs to access the high-fanout network connected to the LE's set, reset, and clock enable signals.

Learn more: Refer to the T55 for information on the location and names of these pins.

#### Global Clock Location

The following tables describe the location of the global clock signals in T55 FPGAs.

**Table 4: Left Clock Input from GPIO Pins**

| Function<br>Name | Resource<br>Name | GCLK[0] | GCLK[1]  | GCLK[2] | GCLK[3] | GCLK[4] | GCLK[5] | GCLK[6] | GCLK[7] |

|------------------|------------------|---------|----------|---------|---------|---------|---------|---------|---------|

| CLK0             | GPIOL_66         | ~       | -        | -       | -       | ~       | -       | -       | -       |

| CLK1             | GPIOL_67         | -       | <b>~</b> | _       | _       | -       | ~       | _       | _       |

| CLK2             | GPIOL_68         | -       | _        | ~       | _       | -       | _       | ~       | _       |

| CLK3             | GPIOL_69         | -       | _        | _       | ~       | -       | _       | -       | ~       |

| CLK4             | GPIOL_70         | ~       | _        | _       | _       | ~       | _       | _       | _       |

| CLK5             | GPIOL_71         | -       | ~        | _       | -       | -       | ~       | -       | _       |

| CLK6             | GPIOL_72         | -       | _        | ~       | -       | -       | _       | ~       | -       |

| CLK7             | GPIOL_73         | -       | -        | _       | ~       | -       | _       | -       | ~       |

**Table 5: Left Clock from PLL OUTCLK Signal**

| PLL<br>Reference | CLKOUT  | GCLK[0] | GCLK[1] | GCLK[2] | GCLK[3] | GCLK[4] | GCLK[5] | GCLK[6] | GCLK[7] |

|------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| PLL_TL0          | CLKOUT0 | ~       | _       | _       | _       | _       | ~       | ~       | -       |

|                  | CLKOUT1 | _       | ~       | _       | ~       | -       | _       | _       | ~       |

|                  | CLKOUT2 | _       | -       | ~       | -       | ~       | _       | _       | -       |

| PLL_BL0          | CLKOUT0 | ~       | -       | _       | ~       | -       | _       | _       | ~       |

|                  | CLKOUT1 | _       | ~       | _       | -       | ~       | _       | ~       | -       |

|                  | CLKOUT2 | _       | _       | ~       | _       | _       | ~       | -       | _       |

**Table 6: Right Clock Input from GPIO Pins**

| Function<br>Name | Resource<br>Name | GCLK[8] | GCLK[9] | GCLK[10] | GCLK[11] | GCLK[12] | GCLK[13] | GCLK[14] | GCLK[15] |

|------------------|------------------|---------|---------|----------|----------|----------|----------|----------|----------|

| CLK0             | GPIOR_181        | ~       | -       | _        | _        | _        | -        | _        | -        |

| CLK1             | GPIOR_180        | -       | ~       | _        | -        | -        | _        | -        | -        |

| CLK2             | GPIOR_179        | -       | -       | ~        | -        | -        | _        | -        | -        |

| CLK3             | GPIOR_178        | _       | -       | _        | ~        | -        | _        | -        | -        |

| CLK4             | GPIOR_177        | _       | _       | _        | _        | ~        | _        | _        | -        |

| CLK5             | GPIOR_176        | _       | _       | _        | _        | -        | ~        | _        | -        |

| CLK6             | GPIOR_175        | _       | _       | _        | _        | _        | _        | ~        | _        |

| CLK7             | GPIOR_174        | _       | -       | _        | _        | _        | _        | _        | ~        |

Table 7: Right Clock from PLL OUTCLK Signal

| PLL<br>Reference | CLKOUT  | GCLK[8] | GCLK[9] | GCLK[10] | GCLK[11] | GCLK[12] | GCLK[13] | GCLK[14] | GCLK[15] |

|------------------|---------|---------|---------|----------|----------|----------|----------|----------|----------|

| PLL_TR0          | CLKOUT0 | ~       | -       | _        | -        | -        | -        | ~        | -        |

|                  | CLKOUT1 | -       | ~       | ~        | -        | -        | _        | -        | -        |

|                  | CLKOUT2 | -       | ~       | ~        | -        | -        | _        | -        | -        |

| PLL_TR1          | CLKOUT0 | ~       | -       | _        | ~        | -        | _        | -        | -        |

|                  | CLKOUT1 | -       | _       | _        | -        | ~        | ~        | -        | -        |

|                  | CLKOUT2 | -       | _       | _        | -        | ~        | ~        | -        | -        |

| PLL_TR2          | CLKOUT0 | ~       | _       | _        | -        | -        | _        | -        | ~        |

|                  | CLKOUT1 | -       | ~       | ~        | -        | -        | _        | -        | -        |

|                  | CLKOUT2 | -       | ~       | ~        | -        | -        | _        | -        | -        |

| PLL_BR0          | CLKOUT0 | -       | -       | _        | ~        | -        | _        | -        | ~        |

|                  | CLKOUT1 | -       | -       | _        | -        | ~        | ~        | -        | -        |

|                  | CLKOUT2 | -       | -       | _        | -        | ~        | ~        | -        | _        |

| PLL_BR1          | CLKOUT0 | -       | -       | ~        | -        | -        | _        | ~        | _        |

|                  | CLKOUT1 | -       | -       | _        | ~        | ~        | _        | -        | -        |

|                  | CLKOUT2 | -       | -       | _        | ~        | ~        | _        | -        | -        |

| PLL_BR2          | CLKOUT0 | -       | -       | _        | -        | -        | ~        | -        | -        |

|                  | CLKOUT1 | -       | ~       | _        | -        | _        | _        | ~        | _        |

|                  | CLKOUT2 | _       | _       | _        | _        | _        | _        | _        | ~        |

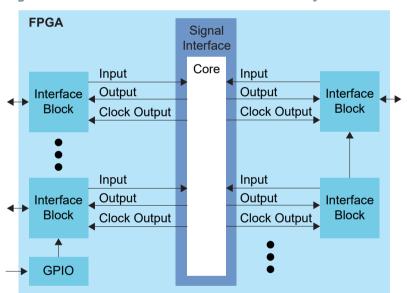

# **Device Interface Functional Description**

The device interface wraps the core and routes signals between the core and the device I/O pads through a signal interface. Because they use the flexible Quantum™ architecture, devices in the Trion® family support a variety of interfaces to meet the needs of different applications.

**Learn more:** The following sections describe the available device interface features in T55 FPGAs. Refer to the Trion® Interfaces User Guide for details on the Efinity® Interface Designer settings.

## Interface Block Connectivity

The FPGA core fabric connects to the interface blocks through a signal interface. The interface blocks then connect to the package pins. The core connects to the interface blocks using three types of signals:

- Input—Input data or clock to the FPGA core

- Output—Output from the FPGA core

- Clock output—Clock signal from the core clock tree

**Figure 6: Interface Block and Core Connectivity**

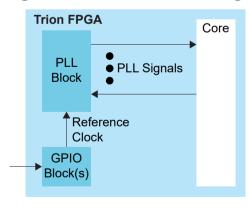

GPIO blocks are a special case because they can operate in several modes. For example, in alternate mode the GPIO signal can bypass the signal interface and directly feed another interface block. So a GPIO configured as an alternate input can be used as a PLL reference clock without going through the signal interface to the core.

When designing for Trion® FPGAs, you create an RTL design for the core and also configure the interface blocks. From the perspective of the core, outputs from the core are inputs to the interface block and inputs to the core are outputs from the interface block.

The Efinity netlist always shows signals from the perspective of the core, so some signals do not appear in the netlist:

GPIO used as reference clocks are not present in the RTL design, they are only visible in the interface block configuration of the Efinity<sup>®</sup> Interface Designer. • The FPGA clock tree is connected to the interface blocks directly. Therefore, clock outputs from the core to the interface are not present in the RTL design, they are only part of the interface configuration (this includes GPIO configured as output clocks).

The following sections describe the different types of interface blocks in the T55. Signals and block diagrams are shown from the perspective of the interface, not the core.

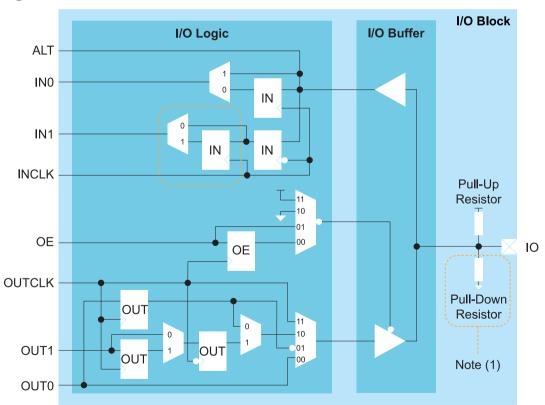

# General-Purpose I/O Logic and Buffer

The GPIO support the 3.3 V LVTTL and 1.8 V, 2.5 V, and 3.3 V LVCMOS I/O standards. The GPIOs are grouped into banks. Each bank has its own VCCIO that sets the bank voltage for the I/O standard.

Each GPIO consists of I/O logic and an I/O buffer. I/O logic connects the core logic to the I/O buffers. I/O buffers are located at the periphery of the device.

The I/O logic comprises three register types:

- Input—Capture interface signals from the I/O before being transferred to the core logic

- Output—Register signals from the core logic before being transferred to the I/O buffers

- Output enable—Enable and disable the I/O buffers when I/O used as output

Table 8: GPIO Modes

| GPIO Mode     | Description                                                                                                                                                                                                                                                                                                               |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input         | Only the input path is enabled; optionally registered. If registered, the input path uses the input clock to control the registers (positively or negatively triggered).                                                                                                                                                  |

|               | Select the alternate input path to drive the alternate function of the GPIO. The alternate path cannot be registered.                                                                                                                                                                                                     |

|               | In DDIO mode, two registers sample the data on the positive and negative edges of the input clock, creating two data streams.                                                                                                                                                                                             |

| Output        | Only the output path is enabled; optionally registered. If registered, the output path uses the output clock to control the registers (positively or negatively triggered).                                                                                                                                               |

|               | The output register can be inverted.                                                                                                                                                                                                                                                                                      |

|               | In DDIO mode, two registers capture the data on the positive and negative edges of the output clock, multiplexing them into one data stream.                                                                                                                                                                              |

| Bidirectional | The input, output, and OE paths are enabled; optionally registered. If registered, the input clock controls the input register, the output clock controls the output and OE registers. All registers can be positively or negatively triggered. Additionally, the input and output paths can be registered independently. |

|               | The output register can be inverted.                                                                                                                                                                                                                                                                                      |

| Clock output  | Clock output path is enabled.                                                                                                                                                                                                                                                                                             |

**Table 9: Supported Features for GPIO and LVDS as GPIO**

LVDS as GPIO are LVDS pins that act as GPIOs instead of the LVDS function.

| Package | GPIO                    | LVDS as GPIO            |

|---------|-------------------------|-------------------------|

| BGA324  | DDIO                    | Variable Drive Strength |

| BGA484  | Schmitt Trigger         | Pull-up                 |

| BGA576  | Variable Drive Strength | Slew Rate               |

|         | Pull-up                 |                         |

|         | Pull-down               |                         |

|         | Slew Rate               |                         |

**Important:** 易灵思<sup>®</sup> recommends that you limit the number of LVDS as GPIO set as output and bidirectional to 14 per bank to avoid switching noise. The Efinity software issues a warning if you exceed the recommended limit.

During configuration, all GPIO pins excluding LVDS as GPIO are configured in weak pull-up mode. The LVDS as GPIO pins are tri-stated without a pull-up or pull-down resistor.

During user mode, unused GPIO pins are tri-stated and configured in weak pull-up mode. You can change the default mode to weak pull-down in the Interface Designer. No glitches if the GPIO is configured as weak pull-up in user mode

**Note:** Refer to Table 67: Single-Ended I/O Buffer Drive Strength Characteristics on page 50 for more information.

### Complex I/O Buffer

Figure 7: I/O Interface Block

1. GPIO pins using LVDS resources do not have a pull-down resistor.

Note: LVDS as GPIO do not have double data I/O (DDIO).

**Table 10: GPIO Signals (Interface to FPGA Fabric)**

| Signal   | Direction | Description                                                                                                                                                                                                                                           |

|----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN[1:0]  | Output    | Input data from the GPIO pad to the core fabric.                                                                                                                                                                                                      |

|          |           | INO is the normal input to the core. In DDIO mode, INO is the data captured on the positive clock edge (HI pin name in the Interface Designer) and IN1 is the data captured on the negative clock edge (LO pin name in the Interface Designer).       |

| ALT      | Output    | Alternative input connection (in the Interface Designer, <b>Register Option</b> is <b>none</b> ).  Alternative connections are GCLK, GCTRL, PLL_CLKIN, MIPI_CLKIN. (3)                                                                                |

| OUT[1:0] | Input     | Output data to GPIO pad from the core fabric.                                                                                                                                                                                                         |

|          |           | OUT0 is the normal output from the core. In DDIO mode, OUT0 is the data captured on the positive clock edge (HI pin name in the Interface Designer) and OUT1 is the data captured on the negative clock edge (LO pin name in the Interface Designer). |

| OE       | Input     | Output enable from core fabric to the I/O block. Can be registered.                                                                                                                                                                                   |

| OUTCLK   | Input     | Core clock that controls the output and OE registers. This clock is not visible in the user netlist.                                                                                                                                                  |

| INCLK    | Input     | Core clock that controls the input registers. This clock is not visible in the user netlist.                                                                                                                                                          |

**Table 11: GPIO Pads**

| Signal | Direction     | Description |

|--------|---------------|-------------|

| Ю      | Bidirectional | GPIO pad.   |

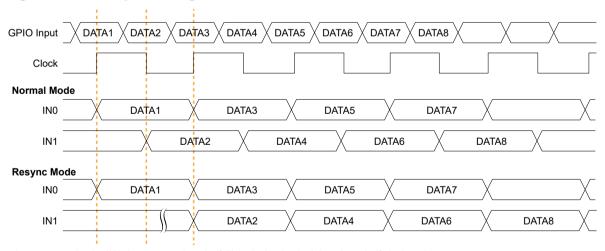

#### Double-Data I/O

T55 FPGAs support double data I/O (DDIO) on input and output registers. In this mode, the DDIO register captures data on both positive and negative clock edges. The core receives 2 bit wide data from the interface.

In normal mode, the interface receives or sends data directly to or from the core on the positive and negative clock edges. In resync mode, the interface resynchronizes the data to pass both signals on the positive clock edge only.

LVDS as GPIO (that is, single ended I/O) do not support DDIO functionality.

**Figure 8: DDIO Input Timing Waveform**

In resync mode, the IN1 data captured on the falling clock edge is delayed one half clock cycle.

In the Interface Designer, IN0 is the HI pin name and IN1 is the LO pin name.

<sup>(3)</sup> MIPI\_CLKIN is only available in packages that support MIPI.

**Normal Mode** Clock OUT0 DATA1 DATA3 DATA5 DATA7 OUT1 DATA2 DATA4 DATA6 DATA8 GPIO Output DATA1 DATA2 DATA3 DATA4 DATA5 DATA6 DATA7 DATA8 Resync Mode Clock OUT0 DATA1 DATA3 DATA5 DATA7 OUT1 DATA2 DATA4 DATA6 DATA8 GPIO Output DATA1 DATA2 DATA3 DATA4 DATA5 DATA6 DATA7 DATA8

Figure 9: DDIO Output Timing Waveform

In the Interface Designer, OUT0 is the HI pin name and OUT1 is the LO pin name.

## I/O Banks

易灵思 FPGAs have input/output (I/O) banks for general-purpose usage. Each I/O bank has independent power pins. The number and voltages supported vary by FPGA and package.

Some I/O banks are merged at the package level by sharing VCCIO pins. Merged banks have underscores (\_) between banks in the name (e.g., 1B\_1C means 1B and 1C are connected).

Table 12: I/O Banks by Package

| Package | I/O Banks                                | Voltage (V)   | Banks with<br>DDIO Support | Merged Banks                  |

|---------|------------------------------------------|---------------|----------------------------|-------------------------------|

| BGA324  | 1A - 1G, 2D - 2F, 3D,<br>TR, BR, 4E - 4F | 1.8, 2.5, 3.3 | Banks 1A-1G,<br>3D, TR, BR | 1B_1C, 1D_1E_1F_1G, 3D_TR_BR  |

| BGA484  | 1A - 1G, 2A - 2F, 3D,<br>TR, BR, 4A - 4F | 1.8, 2.5, 3.3 | Banks 1A-1G,<br>3D, TR, BR | 1B_1C, 1D_1E, 1F_1G, 3D_TR_BR |

| BGA576  | 1A - 1G, 2A - 2F, 3D,<br>TR, BR, 4A - 4F | 1.8, 2.5, 3.3 | Banks 1A-1G,<br>3D, TR, BR | 1B_1C, 1D_1E_1F_1G, 3D_TR_BR  |

Learn more: Refer to the T55 for information on the I/O bank assignments.

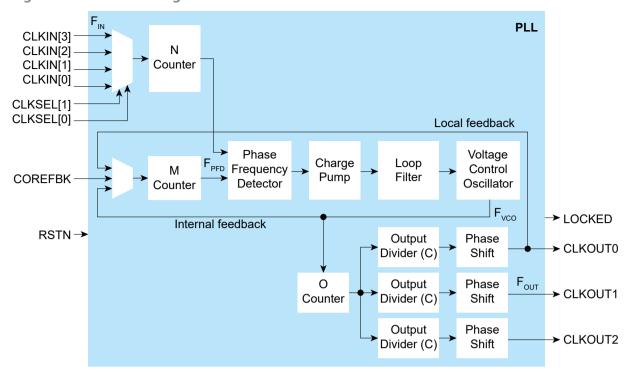

#### PLL

The T55 has 7 or 8 available PLLs (depending on the package) to synthesize clock frequencies.

You can use the PLL to compensate for clock skew/delay via external or internal feedback to meet timing requirements in advanced application. The PLL reference clock has up to four sources. You can dynamically select the PLL reference clock with the CLKSEL port. (Hold the PLL in reset when dynamically selecting the reference clock source.)

Some of the PLLs can use an LVDS RX buffer to input it's reference clock.

The PLL consists of a pre-divider counter (N counter), a feedback multiplier counter (M counter), a post-divider counter (O counter), and output divider.

**Note:** Refer to T55 Interface Floorplan for the location of the PLLs on the die. Refer to Table 96: General Pinouts on page 61 for the PLL reference clock resource assignment.

Figure 10: PLL Block Diagram

The counter settings define the PLL output frequency:

| Internal Feedback Mode                                                                                    | Local and Core Feedback Mode                                                                                                                                                                      | Where:                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $F_{PFD} = F_{IN} / N$ $F_{VCO} = F_{PFD} \times M$ $F_{OUT} = (F_{IN} \times M) / (N \times O \times C)$ | $\begin{aligned} F_{PFD} &= F_{IN} / N \\ F_{VCO} &= (F_{PFD} \times M \times O \times C_{FBK}) \end{aligned} ^{(4)} \\ F_{OUT} &= (F_{IN} \times M \times C_{FBK}) / (N \times C) \end{aligned}$ | $F_{VCO}$ is the voltage control oscillator frequency $F_{OUT}$ is the output clock frequency $F_{IN}$ is the reference clock frequency $F_{PFD}$ is the phase frequency detector input frequency $C$ is the output divider |

Note: F<sub>IN</sub> must be within the values stated in PLL Timing and AC Characteristics on page 57.

Figure 11: PLL Interface Block Diagram

**Table 13: PLL Signals (Interface to FPGA Fabric)**

| Signal      | Direction | Description                                                                   |

|-------------|-----------|-------------------------------------------------------------------------------|

| CLKIN[3:0]  | Input     | Reference clocks driven by I/O pads or core clock tree.                       |

| CLKSEL[1:0] | Input     | You can dynamically select the reference clock from one of the clock in pins. |

<sup>(4) (</sup>M x O x  $C_{FBK}$ ) must be  $\leq 255$ .

| Signal                        | Direction | Description                                                                                                                                                                                                                                                                                                              |

|-------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSTN                          | Input     | Active-low PLL reset signal. When asserted, this signal resets the PLL; when deasserted, it enables the PLL. Connect this signal in your design to power up or reset the PLL. Assert the RSTN pin for a minimum pulse of 10 ns to reset the PLL. Assert RSTN when dynamically changing the selected PLL reference clock. |

| COREFBK                       | Input     | Connect to a clock out interface pin when the the PLL feedback mode is set to core.                                                                                                                                                                                                                                      |

| CLKOUT0<br>CLKOUT1<br>CLKOUT2 | Output    | PLL output. The designer can route these signals as input clocks to the core's GCLK network.                                                                                                                                                                                                                             |

| LOCKED                        | Output    | Goes high when PLL achieves lock; goes low when a loss of lock is detected. Connect this signal in your design to monitor the lock status.                                                                                                                                                                               |

**Table 14: PLL Interface Designer Settings - Properties Tab**

| Parameter                         | Choices      | Notes                                                                                                                                               |

|-----------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Instance Name                     | User defined |                                                                                                                                                     |

| PLL Resource                      |              | The resource listing depends on the FPGA you choose.                                                                                                |

| Clock Source                      | External     | PLL reference clock comes from an external pin.                                                                                                     |

|                                   | Dynamic      | PLL reference clock comes from an external pin or the core, and is controlled by the clock select bus.                                              |

|                                   | Core         | PLL reference clock comes from the core.                                                                                                            |

| Automated<br>Clock<br>Calculation |              | Pressing this button launches the PLL Clock Caclulation window. The calculator helps you define PLL settings in an easy-to-use graphical interface. |

**Table 15: PLL Interface Designer Settings - Manual Configuration Tab**

| Parameter                          | Choices                        | Notes                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset Pin Name                     | User defined                   |                                                                                                                                                                                                                                                                                                                                                         |

| Locked Pin Name                    | User defined                   |                                                                                                                                                                                                                                                                                                                                                         |

| Feedback Mode                      | Internal                       | PLL feedback is internal to the PLL resulting in no known phase relationship between clock in and clock out.                                                                                                                                                                                                                                            |

|                                    | Local                          | PLL feedback is local to the PLL. Aligns the clock out phase with clock in.                                                                                                                                                                                                                                                                             |

|                                    | Core                           | PLL feedback is from the core. The feedback clock is defined by the COREFBK connection, and must be one of the three PLL output clocks. Aligns the clock out phase with clock in and removes the core clock delay.                                                                                                                                      |

| Reference clock<br>Frequency (MHz) | User defined                   |                                                                                                                                                                                                                                                                                                                                                         |

| Multiplier (M)                     | 1 - 255 (integer)              | M counter.                                                                                                                                                                                                                                                                                                                                              |

| Pre Divider (N)                    | 1 - 15 (integer)               | N counter.                                                                                                                                                                                                                                                                                                                                              |

| Post Divider (O)                   | 1, 2, 4, 8                     | O counter.                                                                                                                                                                                                                                                                                                                                              |

| Clock 0, Clock 1,<br>Clock 2       | On, off                        | Use these checkboxes to enable or disable clock 0, 1, and 2.                                                                                                                                                                                                                                                                                            |

| Pin Name                           | User defined                   | Specify the pin name for clock 0, 1, or 2.                                                                                                                                                                                                                                                                                                              |

| Divider (C)                        | 1 to 256                       | Output divider.                                                                                                                                                                                                                                                                                                                                         |

| Phase Shift<br>(Degree)            | 0, 45, 90, 135,<br>180, or 270 | Phase shift CLKOUT by 0, 45, 90, 135, 180, or 270 degrees. 180, and 270 require the C divider to be 2. 45 and 135 require the C divider to be 4. 90 requires the C divider to be 2 or 4. To phase shift 225 degrees, select 45 and invert the clock at the destination. To phase shift 315 degrees, select 135 and invert the clock at the destination. |

| Use as Feedback                    | On, off                        |                                                                                                                                                                                                                                                                                                                                                         |

Table 16: PLL Reference Clock Resource Assignments (BGA324)

| PLL                    | REFCLK0          | REFCLK1                                                                            |

|------------------------|------------------|------------------------------------------------------------------------------------|

| PLL_BL0                | GPIOL_15_PLLIN0  | N/A                                                                                |

| PLL_BR0 <sup>(5)</sup> | GPIOR_186_PLLIN0 | N/A                                                                                |

| PLL_BR1                | GPIOR_187_PLLIN1 | N/A                                                                                |

| PLL_BR2                | GPIOR_188_PLLIN2 | N/A                                                                                |

| PLL_TR0                | GPIOR_166_PLLIN0 | Differential: GPIOT_RXP09_CLKP0, GPIOT_RXN09_CLKN0 Single-ended: GPIOT_RXP09_CLKP0 |

| PLL_TR1                | GPIOR_167_PLLIN1 | Differential: GPIOT_RXP19_CLKP1, GPIOT_RXN19_CLKN1 Single-ended: GPIOT_RXP19_CLKP1 |

| PLL_TR2                | GPIOR_168_PLLIN2 | Differential: GPIOT_RXP29_CLKP2, GPIOT_RXN29_CLKN2 Single-ended: GPIOT_RXP29_CLKP2 |

Table 17: PLL Reference Clock Resource Assignments (BGA484 and BGA576)

| PLL                    | REFCLK0          | REFCLK1                                                                            |

|------------------------|------------------|------------------------------------------------------------------------------------|

| PLL_BL0                | GPIOL_15_PLLIN0  | GPIOL_19_PLLIN1                                                                    |

| PLL_TL0                | GPIOL_164_PLLIN0 | GPIOL_160_PLLIN1                                                                   |

| PLL_BR0 <sup>(6)</sup> | GPIOR_186_PLLIN0 | Differential: GPIOB_RXP09_CLKP0, GPIOB_RXN09_CLKN0 Single-ended: GPIOB_RXP09_CLKP0 |

| PLL_BR1                | GPIOR_187_PLLIN1 | Differential: GPIOB_RXP19_CLKP1, GPIOB_RXN19_CLKN1 Single-ended: GPIOB_RXP19_CLKP1 |

| PLL_BR2                | GPIOR_188_PLLIN2 | Differential: GPIOB_RXP29_CLKP2, GPIOB_RXN29_CLKN2 Single-ended: GPIOB_RXP29_CLKP2 |

| PLL_TR0                | GPIOR_166_PLLIN0 | Differential: GPIOT_RXP09_CLKP0, GPIOT_RXN09_CLKN0 Single-ended: GPIOT_RXP09_CLKP0 |

| PLL_TR1                | GPIOR_167_PLLIN1 | Differential: GPIOT_RXP19_CLKP1, GPIOT_RXN19_CLKN1 Single-ended: GPIOT_RXP19_CLKP1 |

| PLL_TR2                | GPIOR_168_PLLIN2 | Differential: GPIOT_RXP29_CLKP2, GPIOT_RXN29_CLKN2 Single-ended: GPIOT_RXP29_CLKP2 |

<sup>(5)</sup> PLL\_BRO can be used as the PHY clock for DDR DRAM block.

(6) PLL\_BRO can be used as the PHY clock for DDR DRAM block.

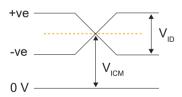

### **LVDS**

The LVDS hard IP transmitters and receivers operate independently.

- LVDS TX consists of LVDS transmitter and serializer logic.

- LVDS RX consists of LVDS receiver, on-die termination, and de-serializer logic.

The T55 has six PLLs for use with the LVDS receiver.

**Note:** You can use the LVDS TX and LVDS RX channels as 3.3 V, 2.5 V, or 1.8 V single-ended GPIO pins, which support a weak pull-up and variable drive strength but do not support a Schmitt trigger. When using LVDS as GPIO, make sure to leave at least 2 pairs of unassigned LVDS pins between any GPIO and LVDS pins. This rule applies for pins on each side of the device (top, bottom, left, right). This separation reduces noise. The Efinity software issues an error if you do not leave this separation.

#### The LVDS hard IP has these features:

- Dedicated LVDS TX and RX channels (the number of channels is package dependent) and six LVDS RX clocks

- Up to 800 Mbps for LVDS data transmit or receive

- Supports serialization and deserialization factors: 8:1, 7:1, 6:1, 5:1, 4:1, 3:1, and 2:1

- · Ability to disable serialization and deserialization

- Source synchronous clock output edge-aligned with data for LVDS transmitter and receiver

- 100 Ω on-die termination resistor for the LVDS receiver

**Note:** The LVDS RX supports the sub-lvds, slvs, HiVcm, RSDS and 3.3 V LVPECL differential I/O standards with a transfer rate of up to 800 Mbps.

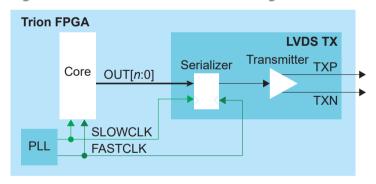

#### LVDS TX

Figure 12: LVDS TX Interface Block Diagram

**Table 18: LVDS TX Signals (Interface to FPGA Fabric)**

| Signal              | Direction | Notes                                                                                                |

|---------------------|-----------|------------------------------------------------------------------------------------------------------|

| OUT[ <i>n</i> -1:0] | Input     | Parallel output data where $n$ is the serialization factor.<br>A width of 1 bypasses the serializer. |

| FASTCLK             | Input     | Fast clock to serialize the data to the LVDS pads.                                                   |

| SLOWCLK             | Input     | Slow clock to latch the incoming data from the core.                                                 |

**Table 19: LVDS TX Pads**

| Pad | Direction | Description         |

|-----|-----------|---------------------|

| TXP | Output    | Differential P pad. |

| TXN | Output    | Differential N pad. |

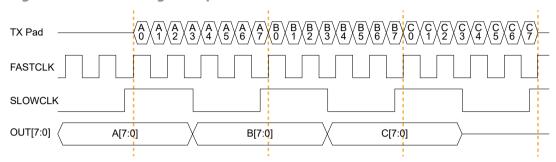

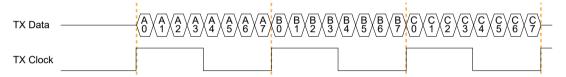

The following waveform shows the relationship between the fast clock, slow clock, TX data going to the pad, and byte-aligned data from the core.

Figure 13: LVDS Timing Example Serialization Width of 8

OUT is byte-aligned data passed from the core on the rising edge of SLOWCLK.

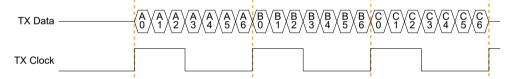

Figure 14: LVDS Timing Data and Clock Relationship Width of 8 (Parallel Clock Division=1)

Figure 15: LVDS Timing Data and Clock Relationship Width of 7 (Parallel Clock Division=1)

**Table 20: LVDS TX Settings in Efinity® Interface Designer**

| Parameters           | Choices                      | Notes                                                                                                                                                                                                 |

|----------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode                 | serial data output           | serial data output—Simple output buffer or serialized output.                                                                                                                                         |

|                      | or reference<br>clock output | <b>reference clock output</b> —Use the transmitter as a clock output. When choosing this mode, the <b>Serialization Width</b> you choose should match the serialization for the rest of the LVDS bus. |

| Parallel Clock       | 1, 2                         | 1—The output clock from the LVDS TX lane is parallel clock frequency.                                                                                                                                 |

| Division             |                              | <b>2</b> —The output clock from the TX lane is half of the parallel clock frequency.                                                                                                                  |

| Enable Serialization | On or off                    | When off, the serializer is bypassed and the LVDS buffer is used as a normal output.                                                                                                                  |

| Serialization Width  | 2, 3, 4, 5, 6, 7, or 8       | Supports 8:1, 7:1, 6:1, 5:1, 4:1, 3:1, and 2:1.                                                                                                                                                       |

| Reduce VOD Swing     | On or off                    | When true, enables reduced output swing (similar to slow slew rate).                                                                                                                                  |

| Output Load          | 3, 5, 7<br>(default), or 10  | Output load in pF. Use an output load of 7 pF or higher to achieve the maximum throughput of 800 Mbps.                                                                                                |

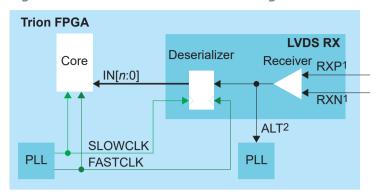

#### LVDS RX

Figure 16: LVDS RX Interface Block Diagram

- 1. There is a ~30k  $\Omega$  internal weak pull-up to VCCIO (3.3V).

- 2. Only available for an LVDS RX resource in bypass mode (deserialization width is 1).

**Table 21: LVDS RX Signals (Interface to FPGA Fabric)**

| Signal             | Direction | Notes                                                                                                                                                                                  |  |

|--------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IN[ <i>n</i> -1:0] | Output    | Parallel input data where <i>n</i> is the de-serialization factor.  A width of 1 bypasses the deserializer.                                                                            |  |

| ALT                | Output    | Alternative input, only available for an LVDS RX resource in bypass mode (deserialization width is 1; alternate connection type). Alternative connections are PLL_CLKIN and PLL_EXTFB. |  |

| FASTCLK            | Input     | Fast clock to de-serialize the data from the LVDS pads.                                                                                                                                |  |

| SLOWCLK            | Input     | Slow clock to latch the incoming data to the core.                                                                                                                                     |  |

**Table 22: LVDS RX Pads**

| Pad | Direction | Description         |  |  |

|-----|-----------|---------------------|--|--|

| RXP | Input     | Differential P pad. |  |  |

| RXN | Input     | Differential N pad. |  |  |

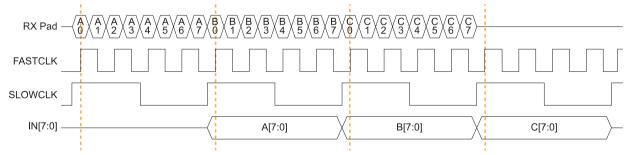

The following waveform shows the relationship between the fast clock, slow clock, RX data coming in from the pad, and byte-aligned data to the core.

Figure 17: LVDS RX Timing Example Serialization Width of 8

IN is byte-aligned data passed to the core on the rising edge of SLOWCLK.

Table 23: LVDS RX Settings in Efinity® Interface Designer

| Parameter                    | Choices                         | Notes                                                                                                |

|------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------|

| Connection Type              | normal, pll_clkin,<br>pll_extfb | normal—Regular RX function.  pll_clkin—Use the PLL CLKIN alternate function of the LVDS RX resource. |

|                              |                                 | <b>pll_extfb</b> —Use the PLL external feedback alternate function of the LVDS RX resource.          |

| Enable<br>Deserialization    | On or off                       | When off, the de-serializer is bypassed and the LVDS buffer is used as a normal input.               |

| Deserialization Width        | 2, 3, 4, 5, 6, 7, or 8          | Supports 8:1, 7:1, 6:1, 5:1, 4:1, 3:1, and 2:1.                                                      |

| Enable On-Die<br>Termination | On or off                       | When on, enables an on-die 100-ohm resistor.                                                         |

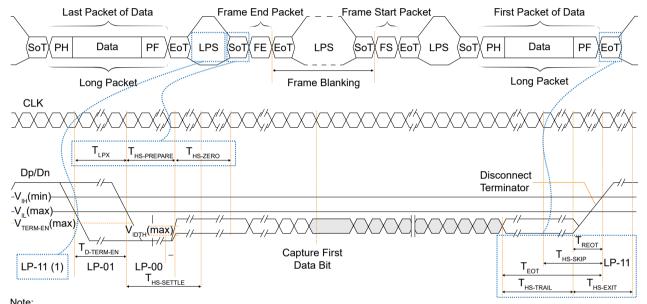

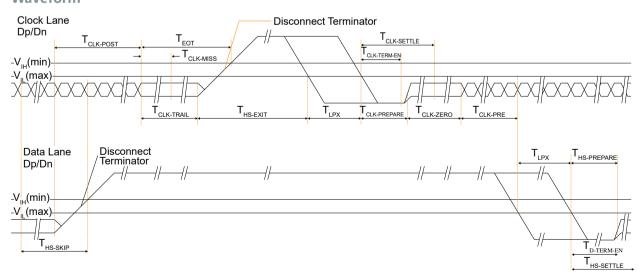

### MIPI

The MIPI CSI-2 interface is the most widely used camera interface for mobile. (7). You can use this interface to build single- or multi-camera designs for a variety of applications.

T55 FPGAs include up to three (depending on the package) hardened MIPI D-PHY blocks (4 data lanes and 1 clock lane) with MIPI CSI-2 IP blocks. The MIPI RX and MIPI TX can operate independently with dedicated I/O banks.

**Note:** The MIPI D-PHY and CSI-2 controller are hard blocks; users cannot bypass the CSI-2 controller to access the D-PHY directly for non-CSI-2 applications.

The MIPI TX/RX interface supports the MIPI CSI-2 specification v1.3 and the MIPI D-PHY specification v1.1. It has the following features:

- Programmable data lane configuration supporting 1, 2, or 4 lanes

- High-speed mode supports up to 1.5 Gbps data rates per lane

- Operates in continuous and non-continuous clock modes

- 64 bit pixel interface for cameras

- Supports Ultra-Low Power State (ULPS)

**Table 24: MIPI Supported Data Types**

| Supported<br>Data Type | Format                                                                                                                     |  |  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| RAW                    | RAW6, RAW7, RAW8, RAW10, RAW12, RAW14                                                                                      |  |  |

| YUV                    | YUV420 8-bit (legacy), YUV420 8-bit, YUV420 10-bit, YUV420 8-bit (CSPS), YUV420 10-bit (CSPS), YUV422 8-bit, YUV422 10-bit |  |  |

| RGB                    | RGB444, RGB555, RGB565, RGB666, RGB888                                                                                     |  |  |

| User Defined           | 8 bit format                                                                                                               |  |  |

<sup>(7)</sup> Source: MIPI Alliance https://www.mipi.org/specifications/csi-2

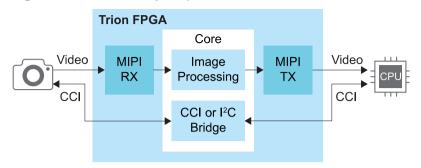

With more than one MIPI TX and RX blocks, Trion® FPGAs support a variety of video applications.

Figure 18: MIPI Example System

#### MIPI TX

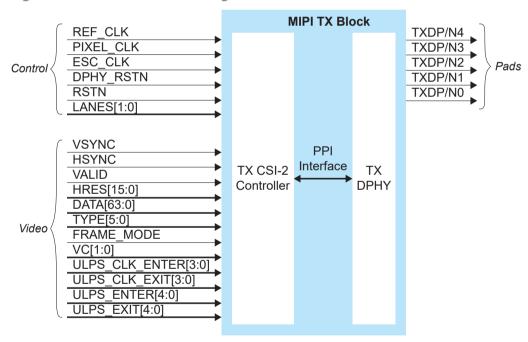

The MIPI TX is a transmitter interface that translates video data from the Trion® core into packetized data sent over the HSSI interface to the board. Five high-speed differential pin pairs (four data, one clock), each of which represent a lane, connect to the board. Control and video signals connect from the MIPI interface to the core.

Figure 19: MIPI TX x4 Block Diagram

The control signals determine the clocking and how many transceiver lanes are used. All control signals are required except the two reset signals. The reset signals are optional, however, you must use both signals or neither.

The MIPI block requires an escape clock (ESC\_CLK) for use when the MIPI interface is in escape (low-power) mode, which runs between 11 and 20 MHz.

Note: 易灵思 recommends that you set the escape clock frequency as close to 20 MHz as possible.

The video signals receive the video data from the core. The MIPI interface block encodes is and sends it out through the MIPI D-PHY lanes.

TXDP/N4

TXDP/N3

TXDP/N2

TXDP/N1

TXDP/N0

Reference

Clock

MREFCLK

GPIO

Figure 20: MIPI TX Interface Block Diagram

**Table 25: MIPI TX Control Signals (Interface to FPGA Fabric)**

**Block**

| Signal     | Direction | Clock Domain | Description                                                                                                                                                                                                                                                                                                             |

|------------|-----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REF_CLK    | Input     | N/A          | Reference clock for the internal MIPI TX PLL used to generate the transmitted data. The FPGA has a dedicated GPIO resource (MREFCLK) that you must configure to provide the reference clock. All of the MIPI TX blocks share this resource.                                                                             |

|            |           |              | The frequency is set using Interface Designer configuration options.                                                                                                                                                                                                                                                    |

| PIXEL_CLK  | Input     | N/A          | Clock used for transferring data from the core to the MIPI TX block. The frequency is based on the number of lanes and video format.                                                                                                                                                                                    |

| ESC_CLK    | Input     | N/A          | Slow clock for escape mode (11 - 20 MHz).                                                                                                                                                                                                                                                                               |

| DPHY_RSTN  | Input     | N/A          | (Optional) Reset for the D-PHY logic, active low. Reset with the controller. See MIPI Reset Timing on page 56.                                                                                                                                                                                                          |

| RSTN       | Input     | N/A          | (Optional) Reset for the CSI-2 controller logic, active low. Typically, you reset the controller with the PHY (see MIPI Reset Timing on page 56). However, when dynamically changing the horizontal resolution, you only need to trigger RSTN (see TX Requirements for Dynamically Changing the Horizontal Resolution). |

| LANES[1:0] | Input     | PIXEL_CLK    | Determines the number of lanes enabled. Can only be changed during reset.  00: lane 0  01: lanes 0 and 1  11: all lanes                                                                                                                                                                                                 |

Table 26: MIPI TX Video Signals (Interface to FPGA Fabric)

| Signal          | Signal Direction Clock Domain |           | Description                                                                                                                                      |  |

|-----------------|-------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VSYNC           | Input                         | PIXEL_CLK | Vertical sync.                                                                                                                                   |  |

| HSYNC           | Input                         | PIXEL_CLK | Horizontal sync.                                                                                                                                 |  |

| VALID           | Input                         | PIXEL_CLK | Valid signal.                                                                                                                                    |  |

| HRES[15:0]      | Input                         | PIXEL_CLK | Horizontal resolution. Can only be changed when VSYNC is low, and should be stable for at least one TX pixel clock cycle before VSYNC goes high. |  |

| DATA[63:0]      | Input                         | PIXEL_CLK | Video data; the format depends on the data type. New data arrives on every pixel clock.                                                          |  |

| TYPE[5:0]       | Input                         | PIXEL_CLK | Video data type. Can only be changed when HSYNC is low, and should be stable for at least one TX pixel clock cycle before HSYNC goes high.       |  |

| FRAME_MODE      | Input                         | PIXEL_CLK | Selects frame format. (8) 0: general frame 1: accurate frame Can only be changed during reset.                                                   |  |

| VC[1:0]         | Input                         | PIXEL_CLK | Virtual channel (VC). Can only be changed when VSYNC is low, and should be stable at least one TX pixel clock cycle before VSYNC goes high.      |  |

| ULPS_CLK_ENTER  | Input                         | PIXEL_CLK | Place the clock lane into ULPS mode. Should not be active at the same time as ULPS_CLK_EXIT. Each high pulse should be at least 5 µs.            |  |

| ULPS_CLK_EXIT   | Input                         | PIXEL_CLK | Remove clock lane from ULPS mode. Should not be active at the same time as ULPS_CLK_ENTER. Each high pulse should be at least 5 µs.              |  |

| ULPS_ENTER[3:0] | Input                         | PIXEL_CLK | Place the data lane into ULPS mode. Should not be active at the same time as ULPS_EXIT[3:0]. Each high pulse should be at least 5 µs.            |  |

| ULPS_EXIT[3:0]  | Input                         | PIXEL_CLK | Remove the data lane from ULPS mode. Should not be active at the same time as ULPS_ENTER[3:0]. Each high pulse should be at least 5 $\mu$ s.     |  |

Table 27: MIPI TX Pads

| Pad       | Direction | Description              |

|-----------|-----------|--------------------------|

| TXDP[4:0] | Output    | MIPI transceiver P pads. |

| TXDN[4:0] | Output    | MIPI transceiver N pads. |

<sup>(8)</sup> Refer to the MIPI Camera Serial Interface 2 (MIPI CSI-2) for more information about frame formats.

Table 28: MIPI TX Settings in Efinity® Interface Designer

| Tab                                                                 | Parameter                                                                                   | Choices                                        | Notes                                                                                                                          |

|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Base                                                                | PHY Frequency (MHz)                                                                         | 80.00 - 1500.00                                | Choose one of the possible PHY frequency values.                                                                               |

|                                                                     | Frequency (reference clock)                                                                 | 6, 12, 19.2, 25, 26,<br>27, 38.4, or 52 MHz    | Reference clock frequency.                                                                                                     |

|                                                                     | Enable Continuous PHY<br>Clocking                                                           | On or Off                                      | Turns continuous clock mode on or off.                                                                                         |

| Control                                                             | Escape Clock Pin Name                                                                       | User defined                                   |                                                                                                                                |

|                                                                     | Invert Escape Clock                                                                         | On or Off                                      |                                                                                                                                |

|                                                                     | Pixel Clock Pin Name                                                                        | User defined                                   |                                                                                                                                |

|                                                                     | Invert Pixel Clock                                                                          | On or Off                                      |                                                                                                                                |

| Lane<br>Mapping                                                     | TXD0, TXD1, TXD2,<br>TXD3, TXD4                                                             | clk, data0, data1,<br>data2, or data3          | Map the physical lane to a clock or data lane.                                                                                 |

|                                                                     | Clock Timer                                                                                 | ,                                              |                                                                                                                                |

| Timing                                                              | T <sub>CLK-POST</sub> T <sub>CLK-TRAIL</sub> T <sub>CLK-PREPARE</sub> T <sub>CLK-ZERO</sub> | Varies depending on<br>the PHY frequency       | Changes the MIPI transmitter timing parameters per the DPHY specification. Refer to <b>D-PHY Timing Parameters</b> on page 34. |

|                                                                     | Escape Clock Frequency<br>(MHz)                                                             | User defined                                   | Specify a number between 11 and 20 MHz.                                                                                        |

|                                                                     | T <sub>CLK-PRE</sub>                                                                        | Varies depending on the escape clock frequency | Changes the MIPI transmitter timing parameters per the DPHY specification. Refer to D-PHY Timing Parameters on page 34.        |

|                                                                     | Data Timer                                                                                  |                                                |                                                                                                                                |

| T <sub>HS-PREPARE</sub> T <sub>HS-ZERO</sub> T <sub>HS-PTRAIL</sub> |                                                                                             | Varies depending on<br>the PHY frequency       | Changes the MIPI transmitter timing parameters per the DPHY specification. Refer to D-PHY Timing Parameters on page 34.        |

27

### MIPI TX Video Data TYPE[5:0] Settings

The video data type can only be changed when HSYNC is low.

Table 29: MIPI TX TYPE[5:0]

| TYPE[5:0] | Data Type               | Pixel Data Bits<br>per Pixel Clock | Pixels per Clock            | Bits per Pixel                    | Maximum Data<br>Pixels per Line |

|-----------|-------------------------|------------------------------------|-----------------------------|-----------------------------------|---------------------------------|

| 0x20      | RGB444                  | 48                                 | 4                           | 12                                | 2,880                           |

| 0x21      | RGB555                  | 60                                 | 4                           | 15                                | 2,880                           |

| 0x22      | RGB565                  | 64                                 | 4                           | 16                                | 2,880                           |

| 0x23      | RGB666                  | 54                                 | 3                           | 18                                | 2,556                           |

| 0x24      | RGB888                  | 48                                 | 2                           | 24                                | 1,920                           |

| 0x28      | RAW6                    | 60                                 | 10                          | 6                                 | 7,680                           |

| 0x29      | RAW7                    | 56                                 | 8                           | 7                                 | 6,576                           |

| 0x2A      | RAW8                    | 64                                 | 8                           | 8                                 | 5,760                           |

| 0x2B      | RAW10                   | 60                                 | 6                           | 10                                | 4,608                           |

| 0x2C      | RAW12                   | 60                                 | 5                           | 12                                | 3,840                           |

| 0x2D      | RAW14                   | 56                                 | 4                           | 14                                | 3,288                           |

| 0x18      | YUV420 8 bit            | Odd line: 64<br>Even line: 64      | Odd line: 8<br>Even line: 4 | Odd line: 8<br>Even line: 8, 24   | 2,880                           |

| 0x19      | YUV420 10 bit           | Odd line: 60<br>Even line: 40      | Odd line: 6<br>Even line: 2 | Odd line: 10<br>Even line: 10, 30 | 2,304                           |

| 0x1A      | Legacy<br>YUV420 8 bit  | 48                                 | 4                           | 8, 16                             | 3,840                           |

| 0x1C      | YUV420 8<br>bit (CSPS)  | Odd line: 64<br>Even line: 64      | Odd line: 8<br>Even line: 4 | Odd line: 8<br>Even line: 8, 24   | 2,880                           |

| 0x1D      | YUV420 10<br>bit (CSPS) | Odd line: 60<br>Even line: 40      | Odd line: 6<br>Even line: 2 | Odd line: 10<br>Even line: 10, 30 | 2,304                           |

| 0x1E      | YUV422 8 bit            | 64                                 | 4                           | 8, 24                             | 2,880                           |

| 0x1F      | YUV422 10 bit           | 40                                 | 2                           | 10, 30                            | 2,304                           |

| 0x30 - 37 | User defined 8 bit      | 64                                 | 8                           | 8                                 | 5,760                           |

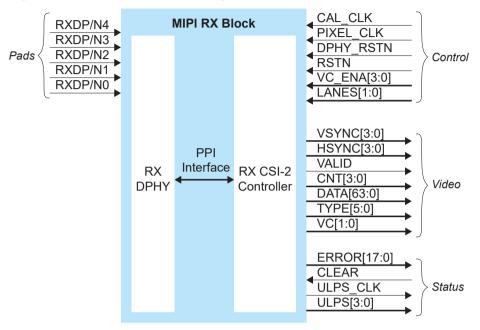

#### MIPI RX

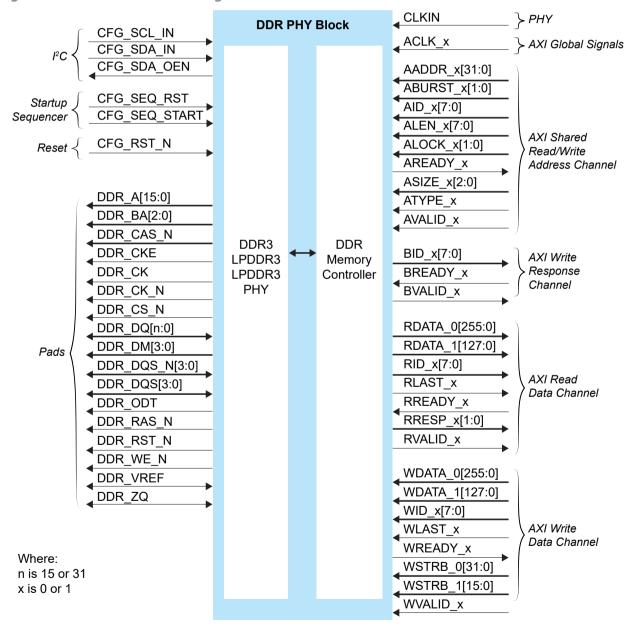

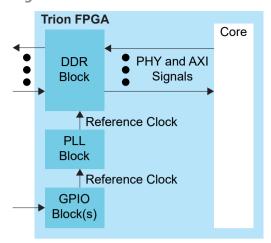

The MIPI RX is a receiver interface that translates HSSI signals from the board to video data in the Trion® core. Five high-speed differential pin pairs (one clock, four data), each of which represent a lane, connect to the board. Control, video, and status signals connect from the MIPI interface to the core.

Figure 21: MIPI RX x4 Block Diagram

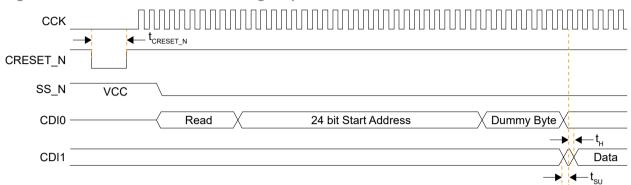

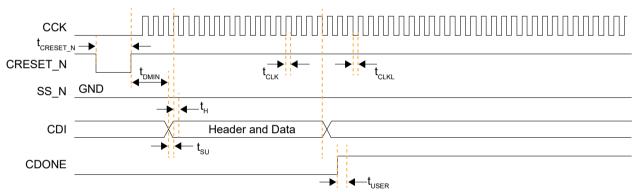

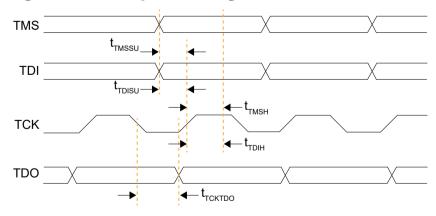

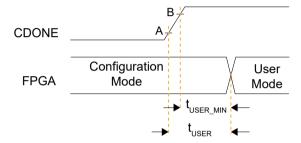

The control signals determine the clocking, how many transceiver lanes are used, and how many virtual channels are enabled. All control signals are required except the two reset signals. The reset signals are optional, however, you must use both signals or neither.