易灵思 的 Sapphire SoC 系列 RISC-V 处理器提供了多种选择,能够满足从超小型软核(Sapphire Lite SoC)到高度可配置软核(Sapphire SoC),再到具备 1 GHz 处理能力的硬核( 高性能 Sapphire SoC)的各种设计需求。Sapphire SoC 具备用户可配置的高性能特性,并支持可选的内存控制器。通过 IP Manager,您可以根据需求配置所需的外设。这种灵活性使 Sapphire SoC 成为各种嵌入式应用的理想选择。

易灵思 RISC-V SoC 配备 32 位 CPU,采用 RISCV32I 指令集架构,支持 M、A、F、D 和 C 扩展,具备六个流水阶段(取指、注入、解码、执行、存储和回写),并且功能可根据需求进行配置。

节能高效

易灵思 FPGA 采用小型化架构,在提供所需性能的同时保持低功耗,非常适合集成到嵌入式系统中。

易于使用

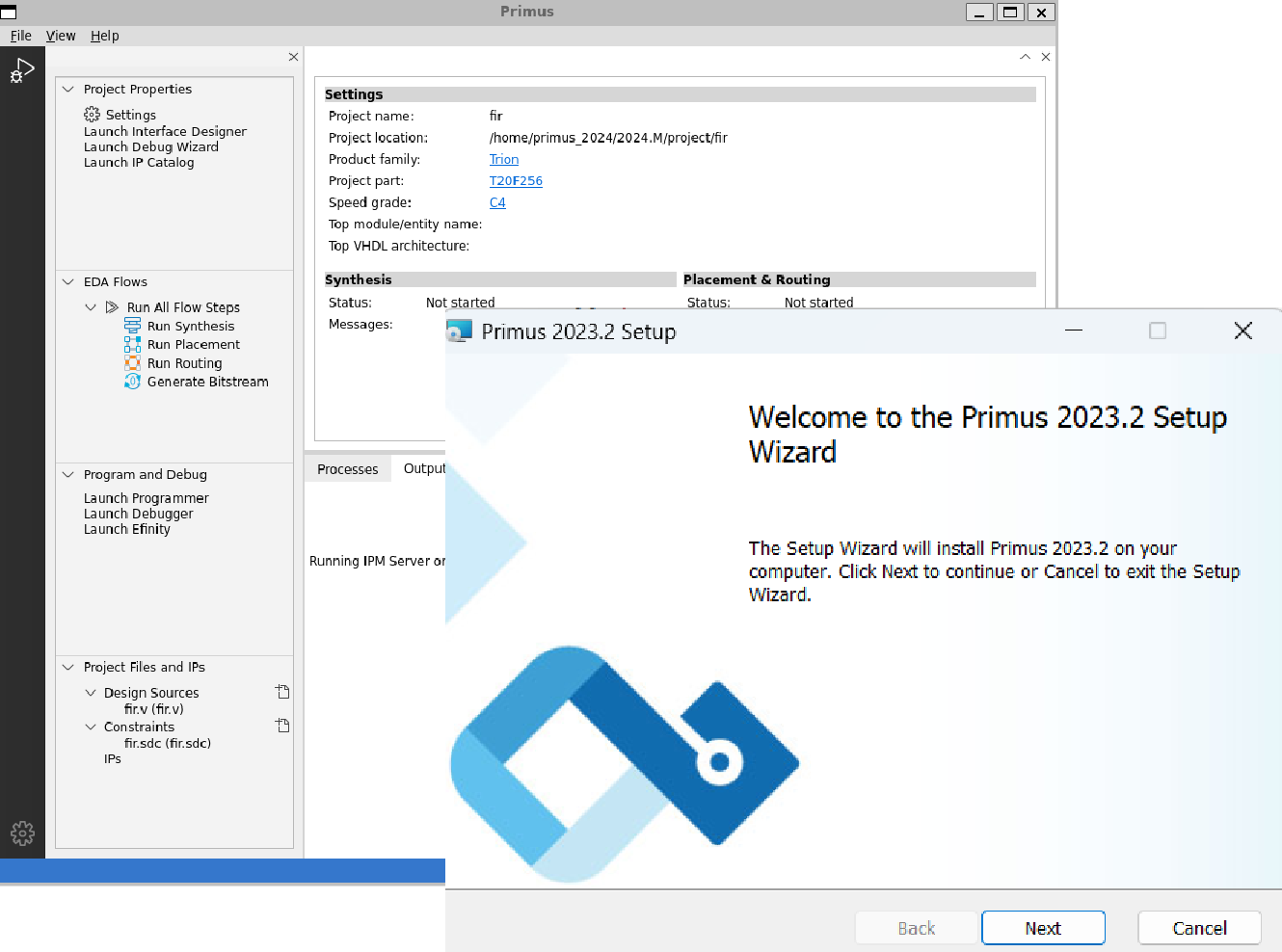

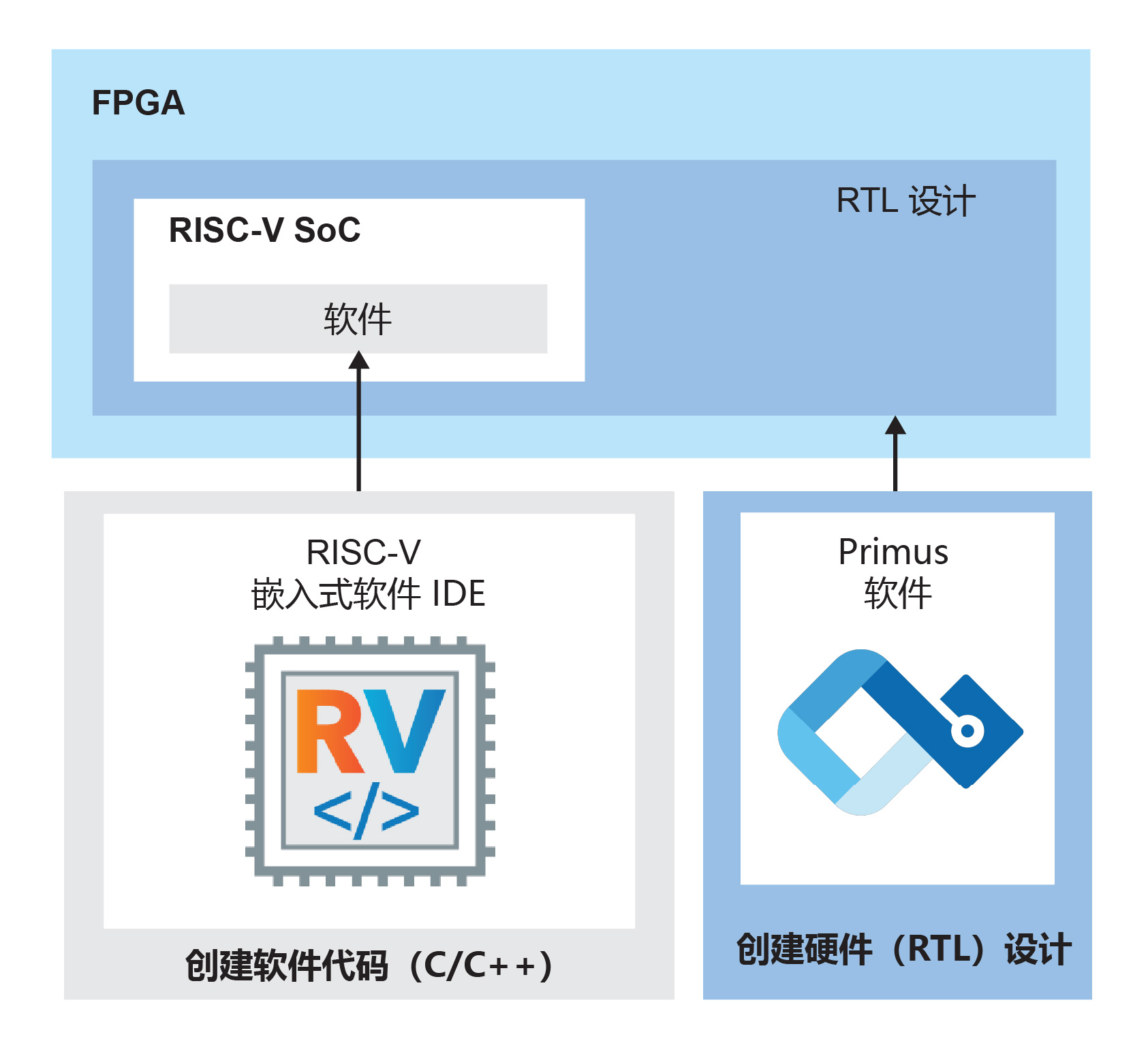

通过 IP Manager 配置 Sapphire SoC,该工具提供直观易用的图形用户界面 (GUI),用户可以选择所需的外设数量以及 CPU 功能。

自定义指令

Sapphire SoC 支持自定义指令接口,您可以通过定制硬件逻辑加速软件功能。

板级支持包 (BSP)

自动生成

在定制 SoC 生成时,软件会自动创建一个板级支持包 (BSP)。使用该 BSP 开发嵌入式软件应用。

Linux 兼容

Sapphire SoC 提供集成的 Buildroot 工具链,自动化的 Linux 内核树生成器,以及驱动程序、用户空间和库示例。

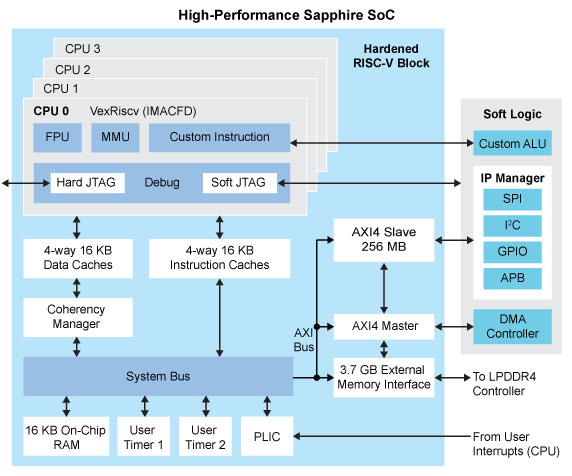

硬核与软核 SoC

Sapphire SoC 系列的 RISC-V 处理器提供了多种选择,从小型软核到具备 1 GHz 性能的硬核处理器。

动态示例设计创建

Sapphire SoC 在用户生成 SoC 后创建示例设计,用户只需编译并编程比特流即可开始开发。示例设计支持 T120F324、Ti60F225 和 Ti180J484 开发套件。

系统管理与通信协议支持

Sapphire SoC 支持 Baremetal、FreeRTOS 和 Linux 解决方案,所有功能均可在单一硬件平台上实现。还支持用户数据报协议 (UDP)、传输控制协议 (TCP)、低功耗蓝牙 (BLE) 和 Wi-Fi。

高性能的硬核 Sapphire RISC-V SoC 提供了多种外设支持接口,如内存控制器、直接内存访问通道、定制指令和 I/O 设备。您可以通过在 IP Manager 中配置 SoC 来选择所需的接口。

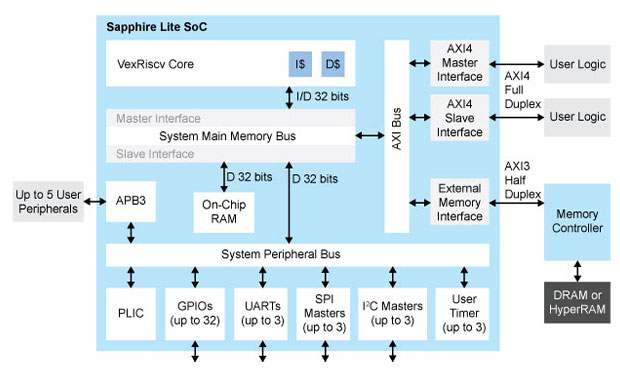

Sapphire SoC 是一款通用的、用户可配置的软核 SoC,支持各种嵌入式应用。

Sapphire Lite SoC 体积最小,非常适合微控制器应用。在最简配置下,它使用的逻辑单元(LE)少于 4K。此精简版本非常适合只需要少量处理能力的场景。

支持的功能

限制