admin 11-13

RISC-V是一个开源的标准指令集架构(ISA,包含基本指令集和可选的扩展集),由非盈利的RISC-V基金会管理。由于RISC-V是免费的和开源的,它已经在世界范围内流行起来,目前有超过65个开源或商用的RISC-V内核。易灵思基于Charles Papon提出的VexRiscv核心创建了RISC-V SoC。

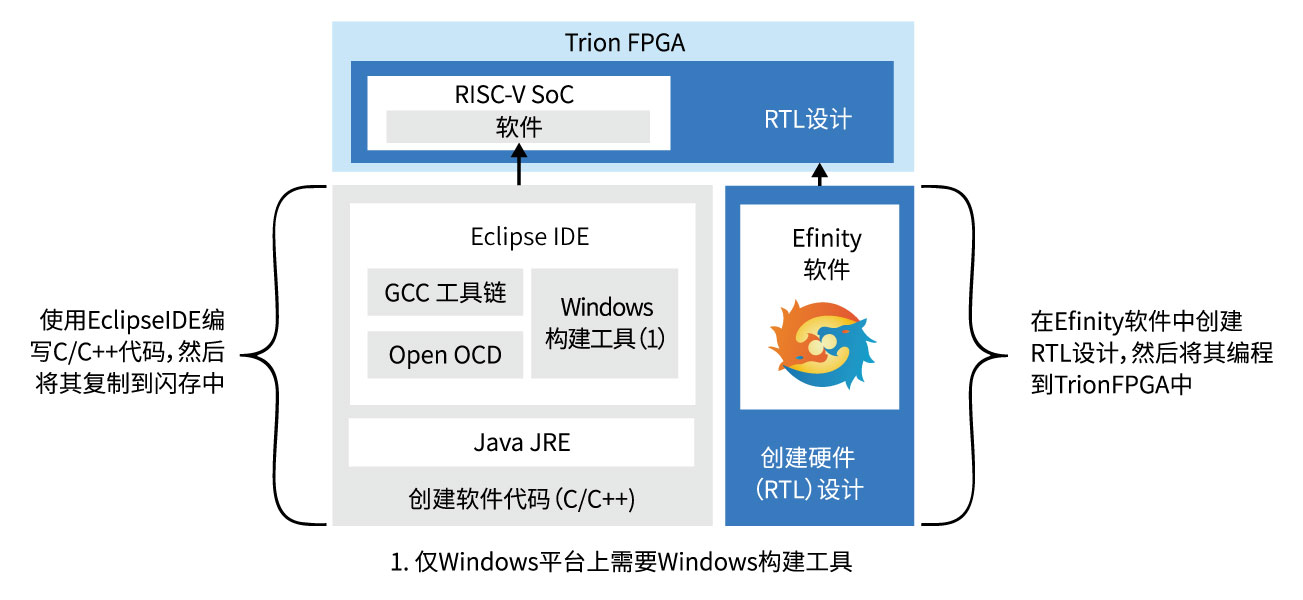

VexRiscv在2018年的RISC-V SoftCPU竞赛中获得第一名,是一个32位CPU,使用ISA RISCV32I具有M和C两种扩展模式,有五级流水(读取、解码、执行、内存和回写),以及一个可配置的特征集。SoC具有RISC-V处理器、内存、一系列I/O和用于嵌入用户功能的接口。您可以轻松地在同一个钛金系列或Trion®系列FPGA中创建包含嵌入式计算和用户定义加速器的完整系统。

Sapphire SoC集成了一个32位RISC-V处理器,该处理器具有多达8路的指令缓存和可配置大小的1-32KB,多达8路的数据缓存和可配置大小的1-32KB,4-512KB的片上RAM,以及各种外设(包含1-5 APB3从站外设和1个AXl从站)。您可以在20-400MHZ范围内配置工作频率(实际性能受设计fMAX的限制)。SoC包括1-3个I2C外设、1-3个UART、1-3个用户定时器和1-3个SPI主器件。还具有浮点单元(FPU)、自定义指令接口和Linux内存管理单元 (MMU)

默认配置具有多达256位半双工AXl总线,可与Elitestek DDR控制器或HyperRAM控制器进行通信。

您可以使用 Efinity®软件中的IP管理器自定义SoC。

对于每个RISC-V SoC, 易灵思提供了一个完整的硬件和软件包。此外,为了帮助您开发软件应用程序,易灵思提供了一组预编译的开源软件。这将帮助您实现: