技术新闻 12-08

一、简介

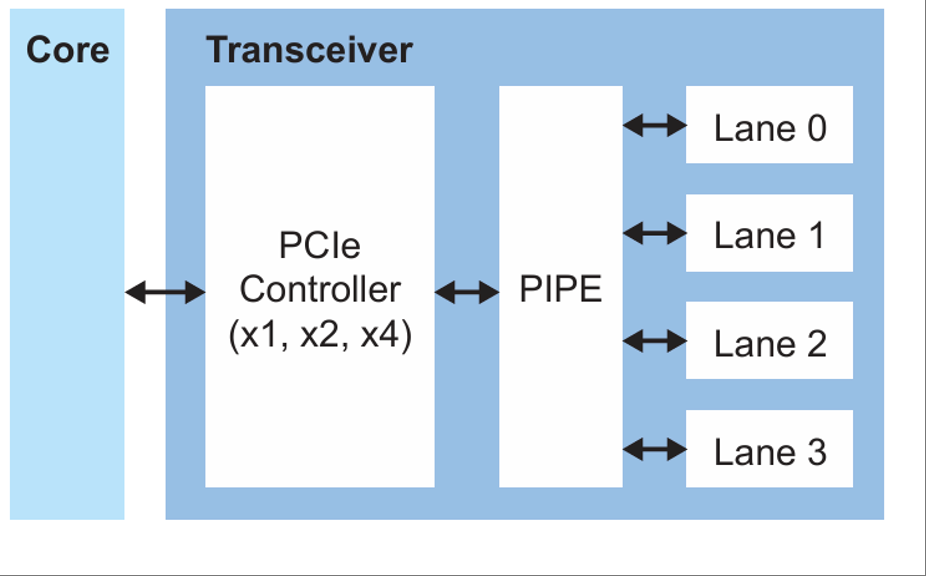

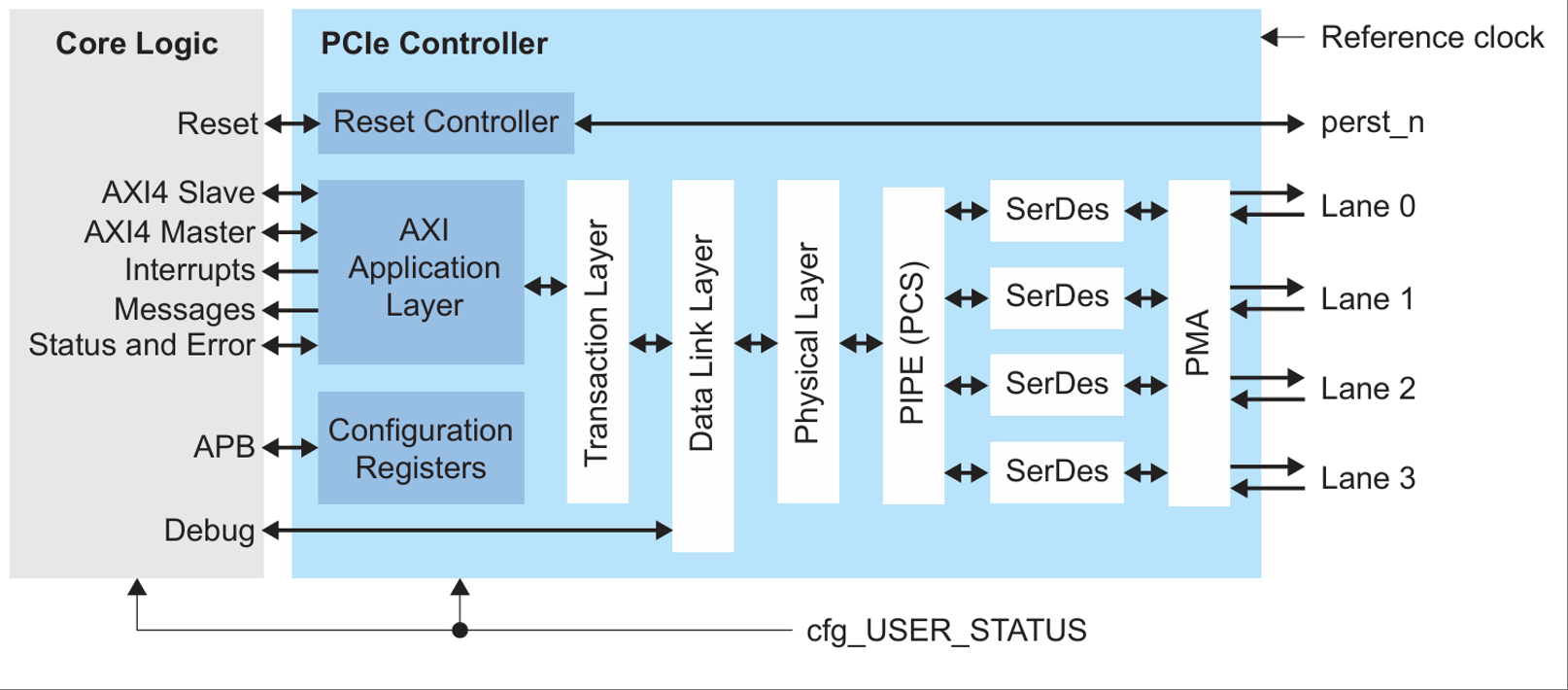

在数字经济飞速发展的今天,数据传输速率已成为硬件性能突破的核心瓶颈。作为国内首款适配中端FPGA的PCIe Gen4高速接口方案,钛金高速接口的闪亮登场,凭借高速低功耗特性、灵活配置能力与全面协议支持,成为FPGA硬件设备实现高速互联的首要选择。其控制器硬件架构由物理介质附加层(PMA)和物理编码子层(PCS)两大核心模块组成,其中PCS硬核支持SGMII、10GBase-R、PCIe Gen4及PMA Direct等多种协议。

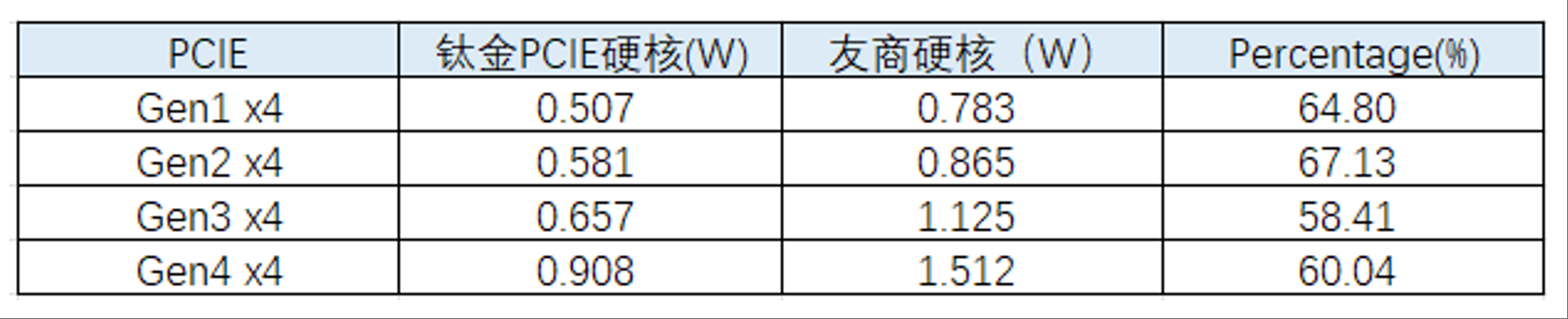

从性能参数来看,钛金PCIe控制器的硬实力尤为突出:其最高支持Gen4 x4的链路配置,单Lane速率可达16Gbps,整个链路的理论带宽最高可达64Gbps,相比友商的PCIe Gen3(单Lane 8Gbps)实现了速率翻倍,意味着数据传输效率直接翻倍提升;且单芯片可支持两个PCIe硬核控制器,能够轻松应对大型文件传输、高清视频流处理、算力密集型计算等高速数据交互场景。

在工作模式上,这款控制器提供了极强的灵活性,可根据实际应用需求配置为端点(EP)模式或根端口(RP)模式,适配不同的硬件拓扑架构。从数据流向来看,用户侧发起的PCIe操作会通过AXI4从端口驱动,而主机侧发起的操作则由AXI4主端口承载,这种双端口设计让控制器既能作为“数据接收端”响应外部请求,也能作为“数据发起端”主动发起交互,完美适配复杂系统中的数据交互需求。

无论是服务器、工业控制设备,还是高端显卡、存储阵列,钛金PCIe Gen4控制器都能凭借其低功耗、高速率、高兼容性的优势,成为连接硬件组件的“高速桥梁”。接下来,我们将深入解析其核心特性与技术细节,带大家全面认识这款PCIe硬核控制器。

二、核心特性

基于钛金PCIe控制器的硬件架构与协议支持,其核心特性围绕“高速、灵活、稳定、低耗”四大维度展开,既充分发挥了PCIe Gen4的协议优势,又针对实际应用场景进行了深度优化,具体特性如下:

2.1 极致速率与带宽,释放Gen4潜力

控制器最高支持PCIe Gen4 x4链路配置,单Lane传输速率稳定在16Gbps,链路总带宽可达64Gbps。这一性能指标意味着数据传输延迟大幅降低,单位时间内可传输的数据量翻倍,能够满足算力密集型场景(如AI推理、高性能计算)和大数据吞吐场景(如分布式存储、4K/8K视频编辑)的核心需求。相比友商产品,无需通过增加链路数量即可实现带宽翻倍提升,有效降低了硬件设计的复杂度与成本。在PCIe Gen4 x4硬核读写带宽测试中,写速度持续超过7500MB/s,读速度持续超过7400MB/s。

2.2 双模式配置 + AXI4-MM接口,适配多元场景

支持端点(EP)和根端口(RP)两种工作模式,可灵活融入不同的系统拓扑。EP模式下,控制器作为外设接口与主机互联(如显卡、网卡等外设场景);RP模式下,控制器可作为系统主控制器连接多个外设(如SSD、WiFi6等主控场景)。同时,通过AXI4-MM主/从端口实现数据交互,AXI4-MM协议作为业界主流的高性能总线协议,具备突发传输、乱序访问等优势,能够与FPGA逻辑架构高效协同,提升系统整体数据处理效率。

2.3 完整中断与消息机制,保障信号响应及时

配备专用中断接口和带内消息中断接口,全面支持传统中断、MSI和MSI-X三种中断模式。传统中断适用于简单场景的信号反馈,MSI通过将中断封装为消息包传输,减少了中断请求的资源占用,而MSI-X则支持更多独立中断向量,能为多设备、多任务场景提供精准的中断响应。三种模式的灵活适配,确保了从简单工业控制到复杂服务器系统等不同场景下,设备状态变化都能被及时捕获和处理。

2.4 虚拟化与多功能支持,应对复杂系统需求

支持SR-IOV(单根I/O虚拟化)技术,最多可配置4个物理函数(PF),每个物理函数又能支持多达16个虚拟函数(VF),总计支持64个虚拟函数。这一特性让单块PCIe设备能被多个虚拟机共享,无需为每个虚拟机配置独立硬件,大幅提升了服务器等虚拟化场景的硬件利用率。同时,多PF/VF的配置能力也让控制器能同时承载多个独立的业务负载,满足复杂系统的多功能集成需求。

2.5 高级错误报告与流量优化,提升系统可靠性

具备高级错误报告(AER)功能,能够实时监测传输过程中的各类错误并详细记录错误类型、位置等信息,方便工程师快速定位故障根源,降低系统维护成本。同时支持TLP处理提示(TPH)和路由标签(Steering Tag)技术,TPH能让主机提前知晓数据包的处理优先级,优化缓存利用效率;路由标签则可实现数据包的精准路由,避免传输拥堵,进一步提升了数据传输的流畅性和系统稳定性。

2.6 灵活复位与电源管理,平衡性能与功耗

支持功能级复位(FLR)和多种电源管理状态,FLR允许只复位单个PCIe功能而不影响整个链路或其他功能,特别适合多设备共享链路的场景(如服务器多网卡配置),避免了局部故障导致整体系统重启。电源管理方面则覆盖L0s、L1、L1子状态及L2等多种低功耗模式,可根据系统负载动态调整功耗,在保证高性能的同时降低待机或轻载状态下的能源消耗,适配移动设备、工业控制器等对功耗敏感的场景。在实际运行功耗测试中,功耗优于友商40%左右。

三、功能描述

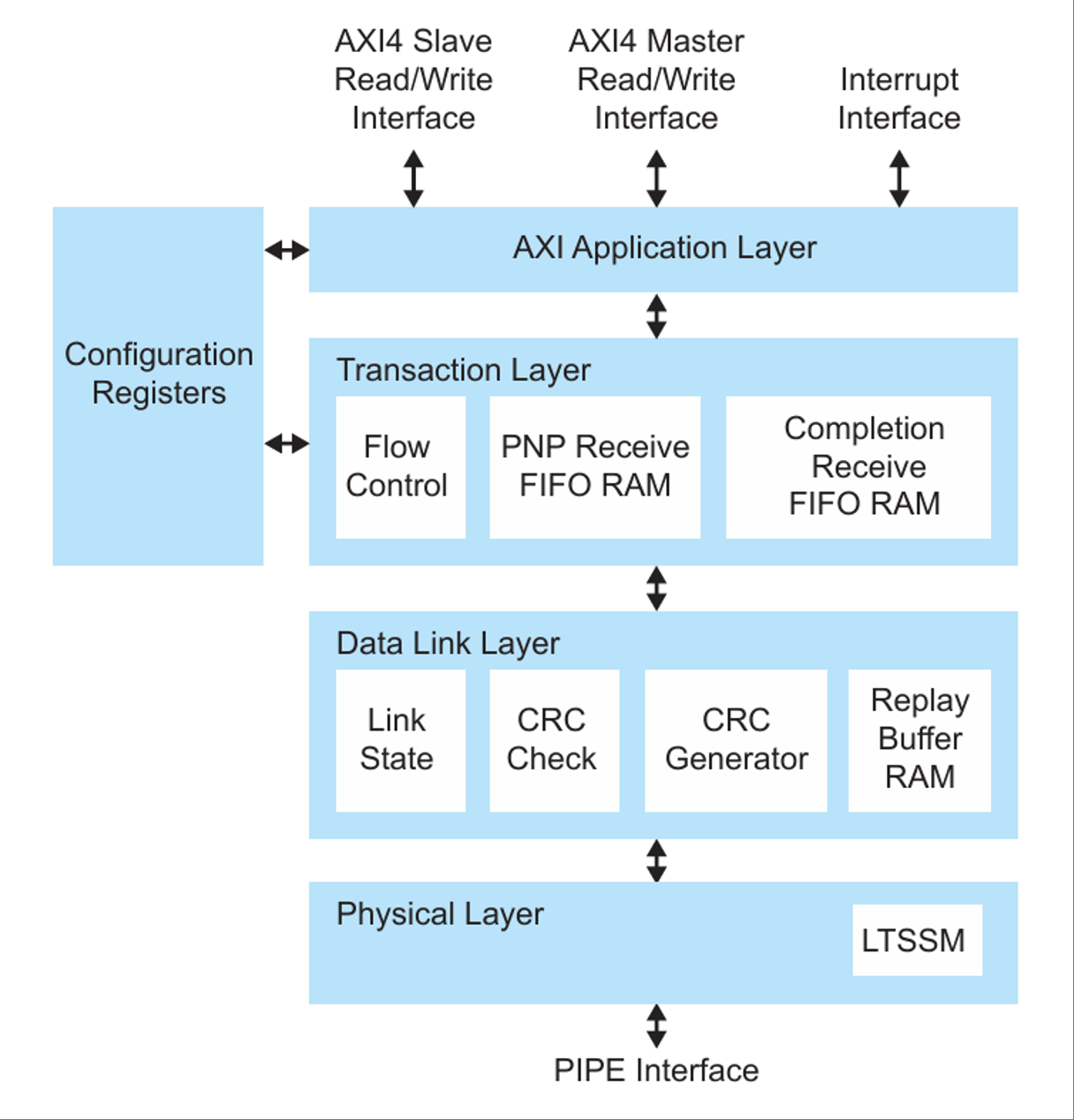

PCIe协议的核心优势在于其清晰的分层架构设计,钛金PCIe硬核控制器严格遵循这一架构,通过物理层、数据链路层、事务层的协同工作,实现了高速、可靠的数据传输。这三层架构如同“高速物流系统”:物理层是“运输公路”,负责数据的物理传输;数据链路层是“物流调度中心”,保障数据传输的完整性;事务层是“快递分拣中心”,负责数据的定向分发。下面我们逐一拆解各层的工作机制。

3.1物理层

物理层是PCIe数据传输的物理载体,完成PCS到PMA之间的数据交互,处理传输过程中的信号同步、失真校准等问题。钛金PCIe硬核控制器的物理层设计充分适配Gen4的高速特性,具体工作流程如下:

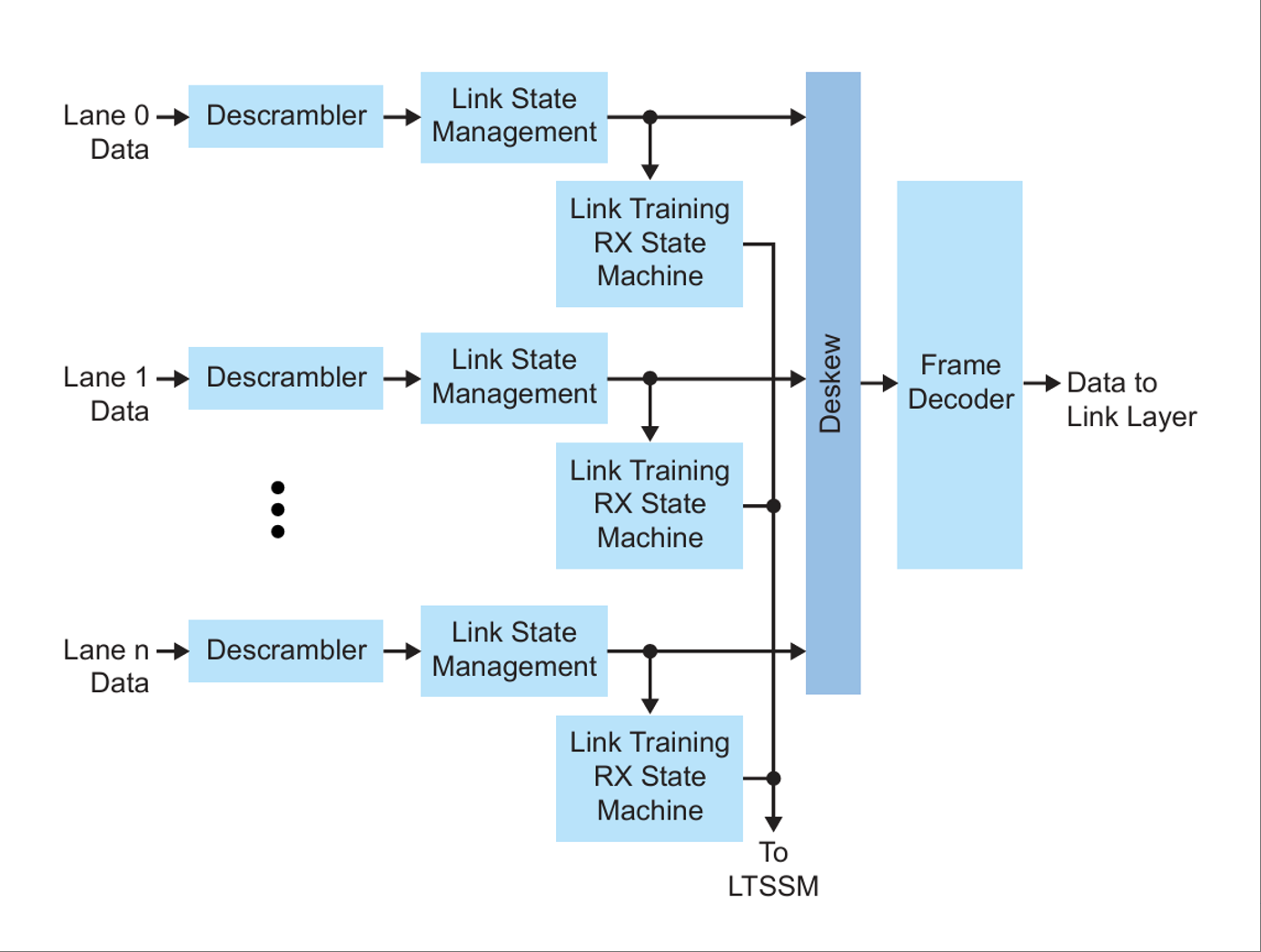

3.1.1接收(RX)侧工作流程

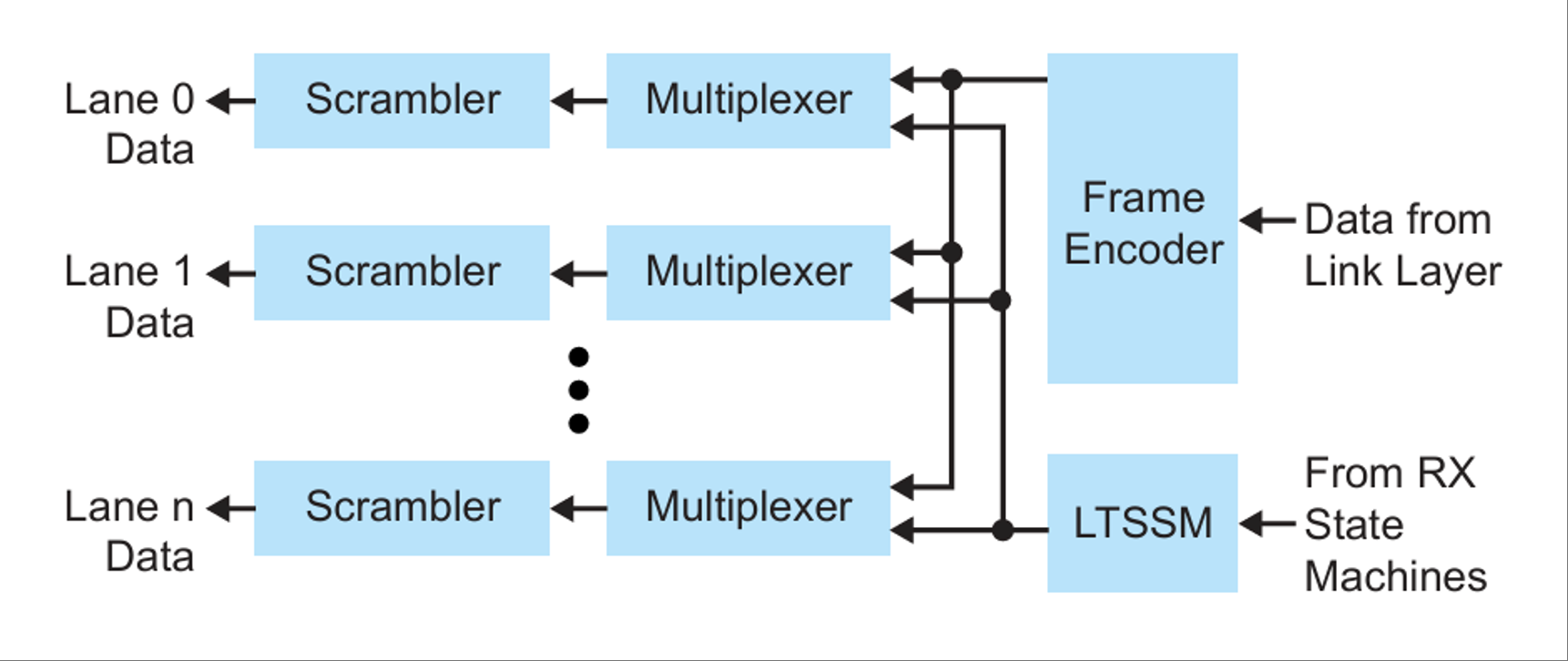

3.1.2发送(TX)侧工作流程

3.1.3关键技术:SRIS与 RX Lane Margining

3.1.4链路训练与状态机(LTSSM)

物理层的核心控制逻辑是LTSSM,负责链路初始化、速率协商、状态监测等关键操作。上电或复位后,LTSSM会自动与对端设备进行协商,确定链路速率(如Gen4 16Gbps)、链路宽度(如x4)等参数,并通过训练序列校准信号时序,确保链路稳定后再进入数据传输状态。若传输过程中出现信号异常,LTSSM会自动触发链路恢复流程,若恢复失败则会通知上层进行错误处理,是保障物理层可靠性的“核心大脑”。

3.2 数据链路层

数据链路层位于物理层与事务层之间,核心职责是保障数据传输的完整性和有序性,相当于为数据传输添加了“安全防护网”,主要通过以下机制实现:

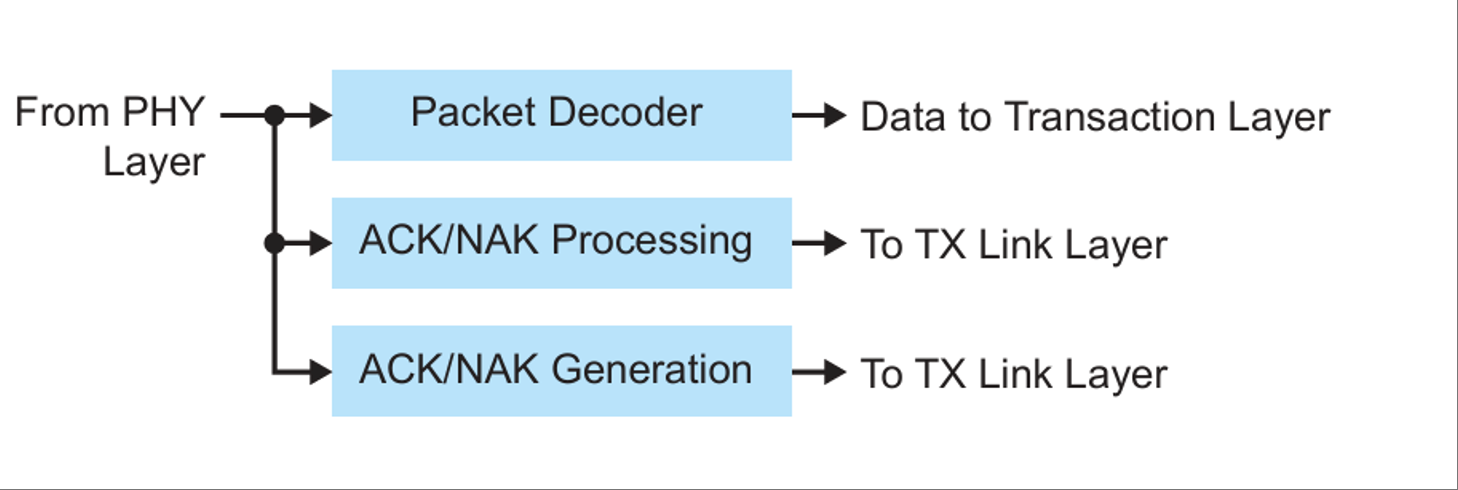

3.2.1接收(RX)侧工作流程

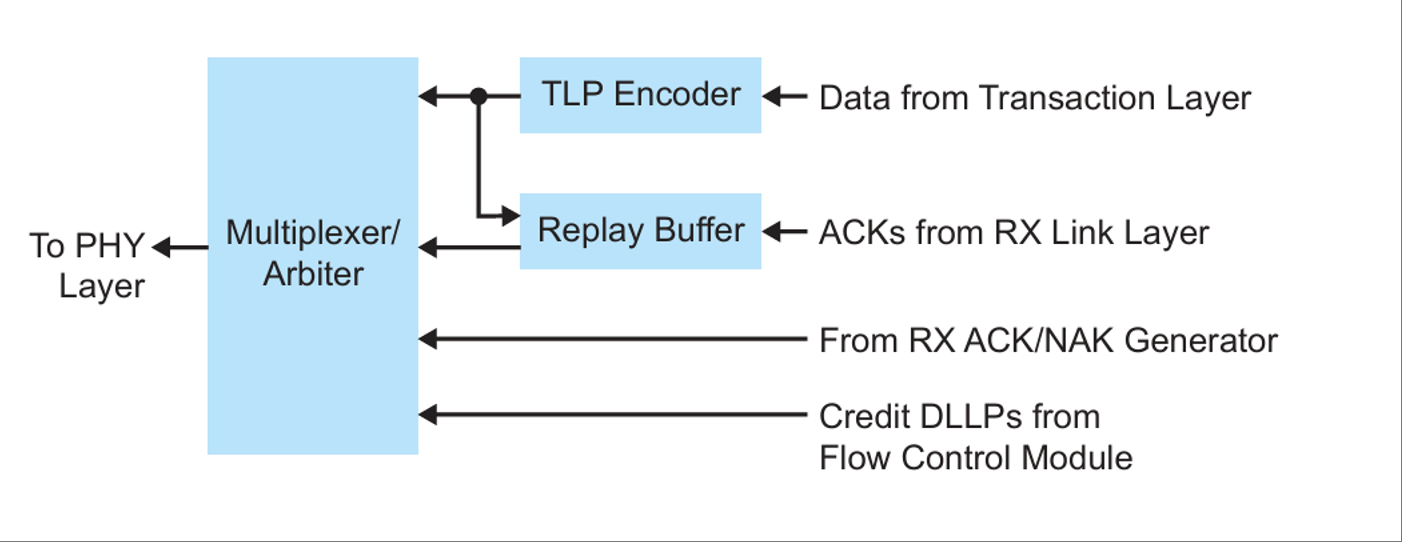

3.2.2发送(TX)侧工作流程

3.2.3核心机制:流量控制与重传保障

3.2.4数据链路层特性交换与流量控制扩展

3.2.5 ACK聚合:提升传输效率

控制器支持ACK DLLP聚合功能,优化传输效率:正常情况下,每个接收的TLP对应一个ACK DLLP;若发送端正忙于传输TLP,ACK DLLP会等待当前TLP传输完成后发送。若等待期间收到新的TLP,控制器会将多ACK DLLP聚合为一个,携带最高序列号,减少DLLP的传输数量,节省链路带宽。

3.3 事务层

事务层是PCIe硬核的“上层大脑”,负责数据包的解析、路由、调度,以及与应用层(如AXI接口)的交互,核心是将应用层的请求转换为PCIe协议支持的TLP,同时将接收的TLP转换为应用层可识别的数据格式。

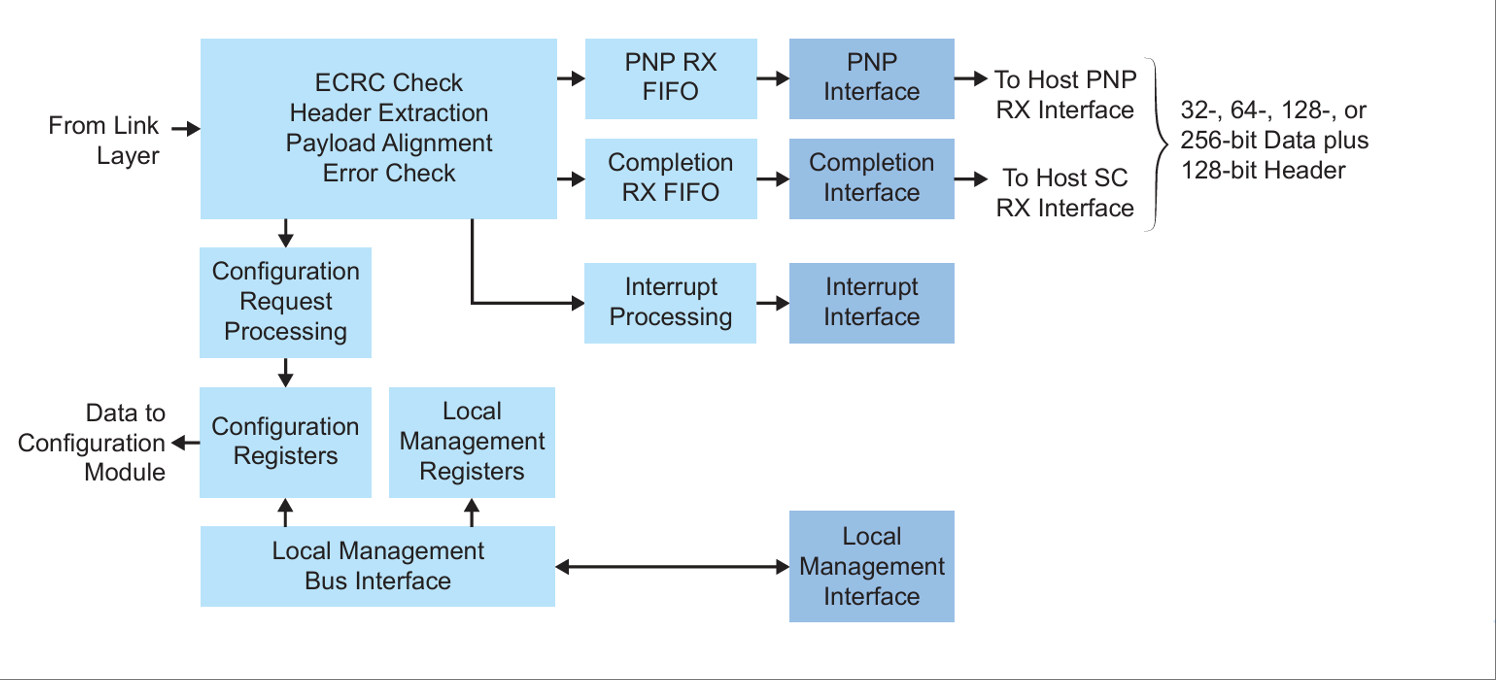

3.3.1接收(RX)侧工作流程

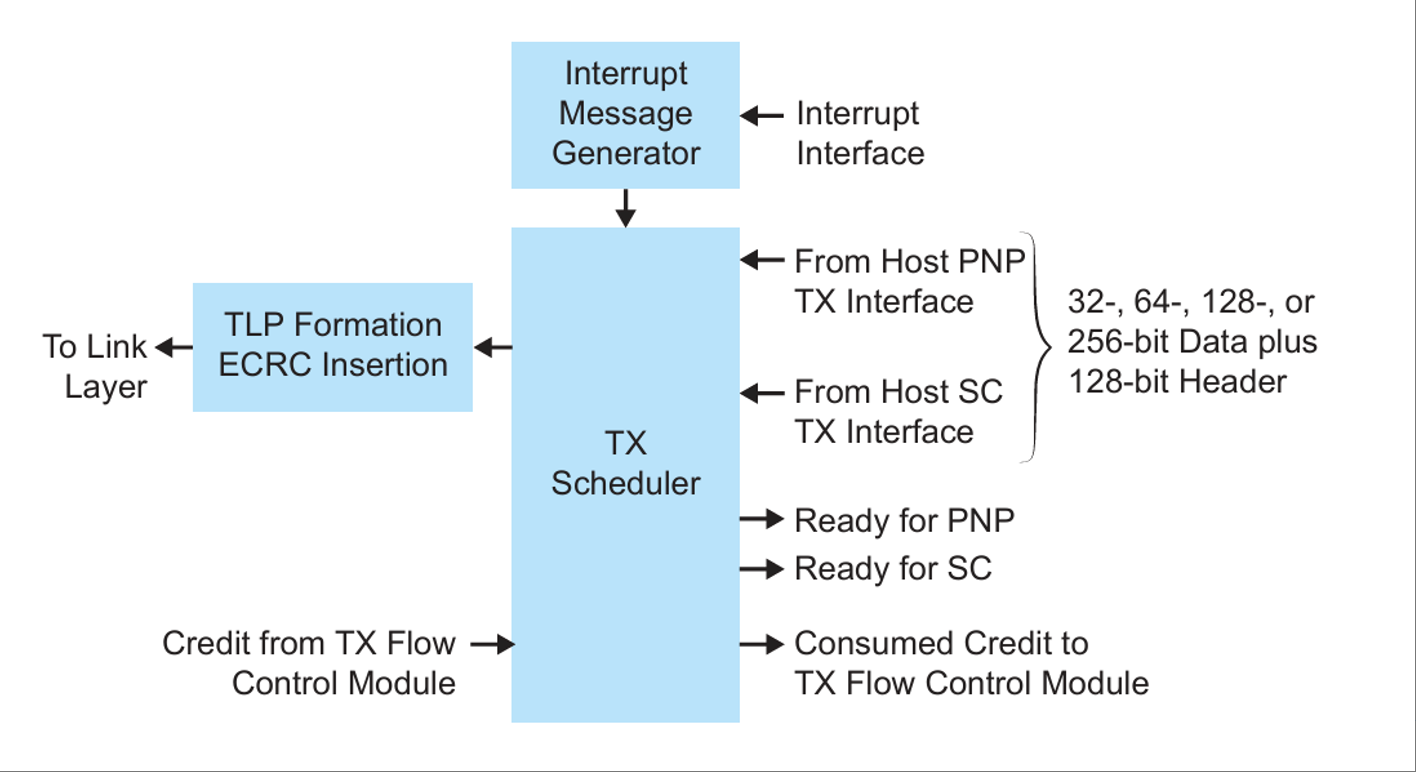

3.3.2发送(TX)侧工作流程

3.3.3核心价值:灵活适配与精准路由

事务层的设计核心是“适配性”和“高效性”:通过对不同类型请求的分类处理,适配内存访问、I/O控制、配置管理等多种应用场景;通过优先级调度和独立接口设计,避免传输拥堵;通过TLP头部的精准编码,实现数据包的定向路由,确保数据能准确送达目标设备或应用模块,是连接应用层与底层传输的“关键桥梁”。

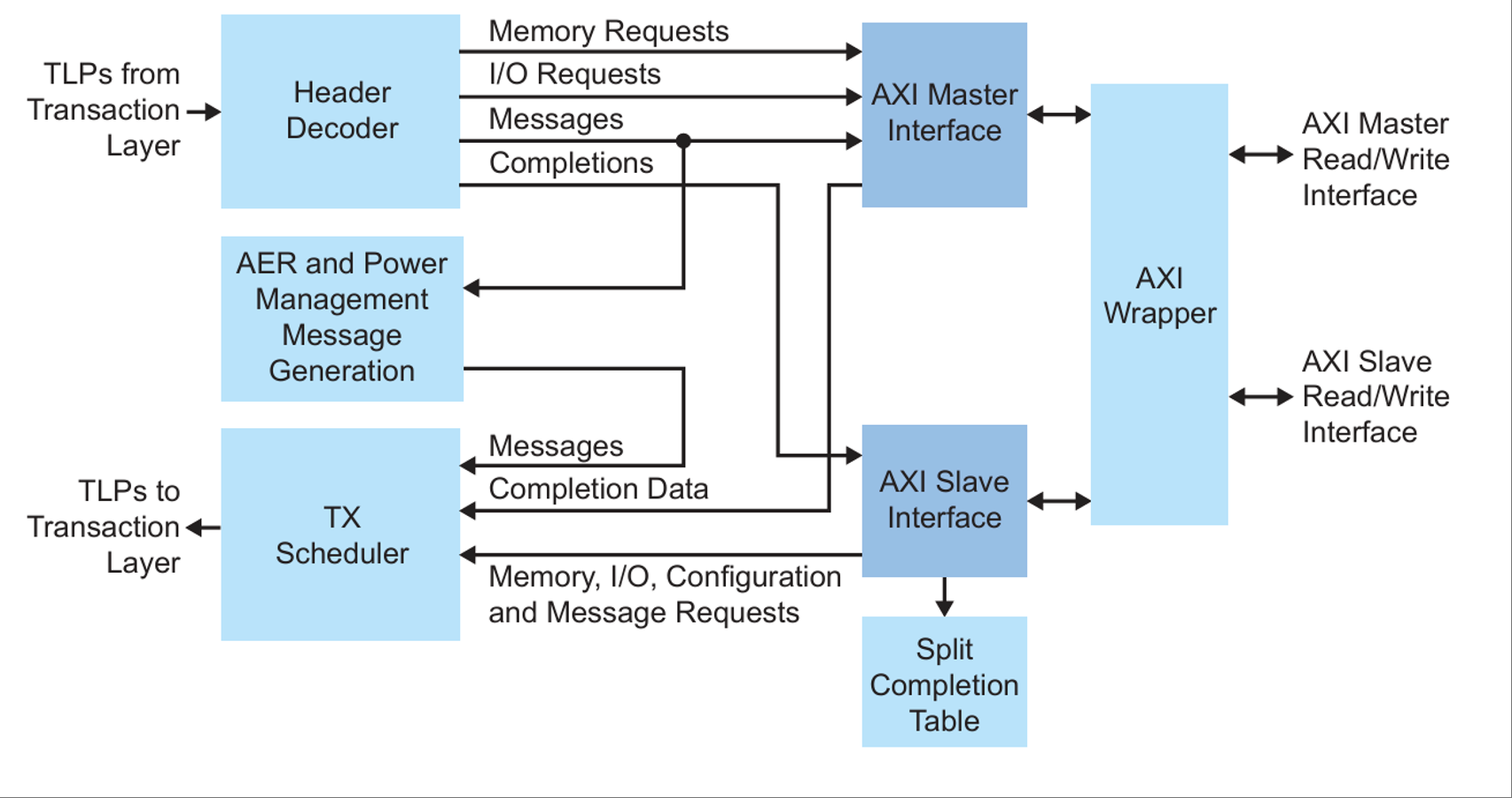

3.4 AXI 应用层

AXI(Advanced eXtensible Interface)作为ARM推出的高性能总线协议,是钛金PCIe控制器连接用户逻辑(如FPGA内部模块、DMA引擎、内存控制器)的核心接口。简单来说,AXI应用层就像一位“翻译官”——将PCIe协议TLP(事务层数据包)转换为AXI信号,让用户逻辑无需理解复杂的PCIe协议就能直接交互;同时也能将用户逻辑的AXI请求转换为TLP,发送到PCIe链路上。

AXI 应用层包含三大核心接口,分工明确:

3.4.1 AXI 主接口读操作:数据从PCIe到用户逻辑的“按需提取”

AXI主接口读操作负责将主机发起的“读请求TLP”转换为AXI信号,从用户逻辑中读取数据并返回给主机。读操作是“分裂事务”(地址和数据通道分离),就像先提交“取件单”(地址),再领取“包裹”(数据),流程清晰且高效。

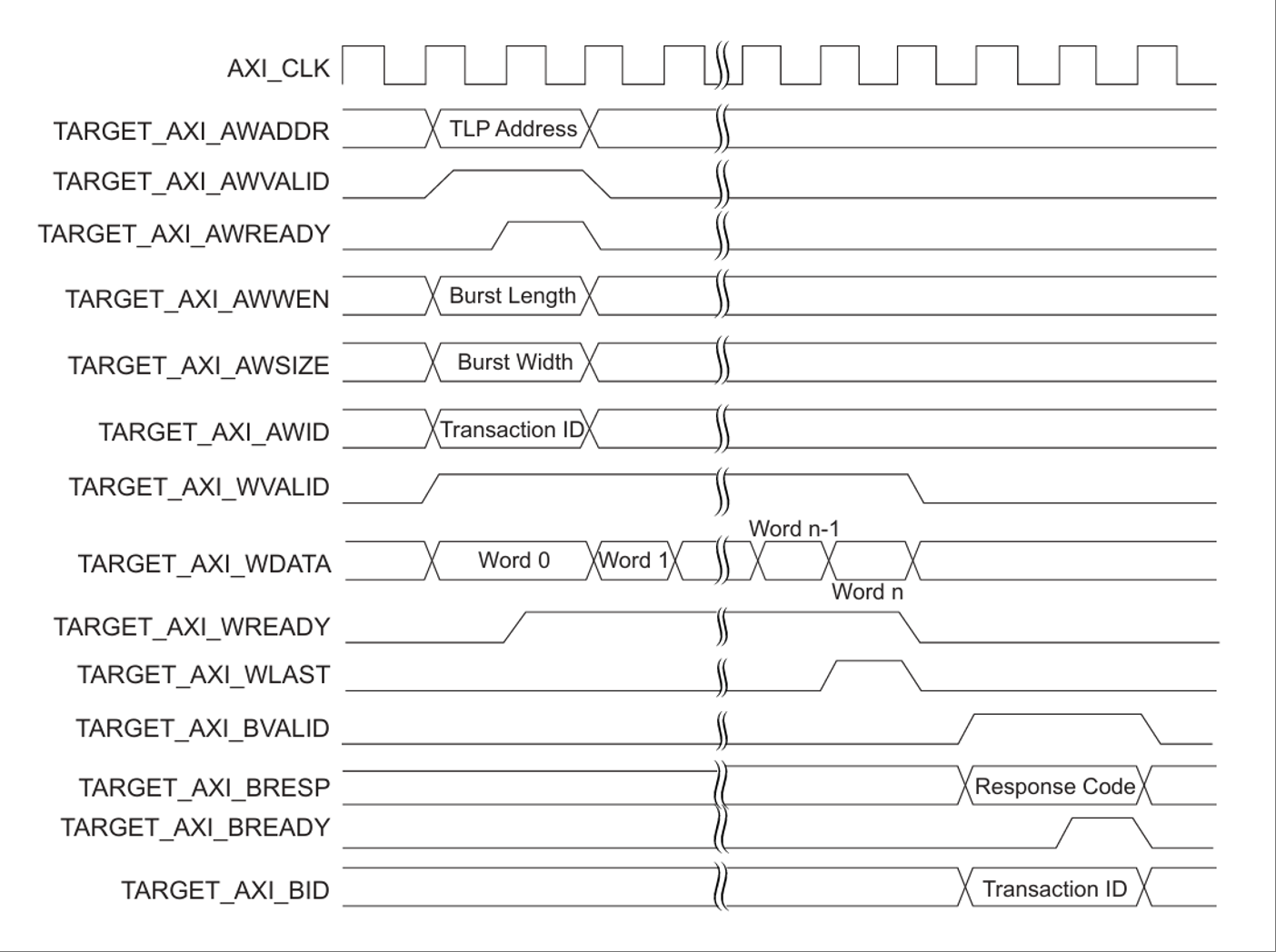

3.4.2 AXI 主接口写操作:数据从PCIe到用户逻辑的“精准投递”

AXI主接口写操作负责将PCIe链路上收到的“写请求TLP”转换为AXI信号,最终写入用户逻辑的内存或寄存器。与读操作的“地址先发、数据后到”不同,写操作的地址和数据通道是并行的,就像“快递单”和“包裹”同时发出,效率更高。

写操作的基本流程

关键特性与特殊场景

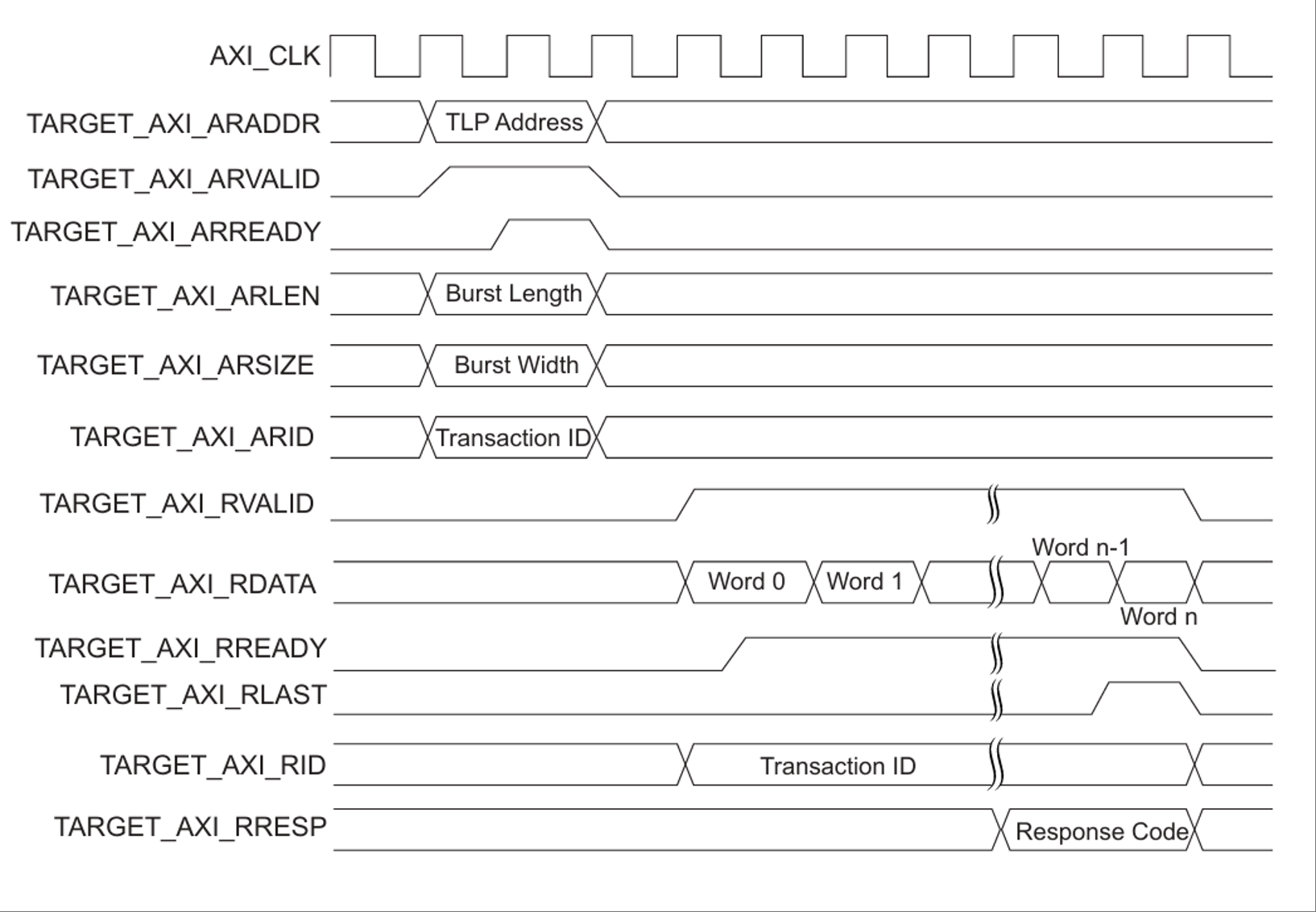

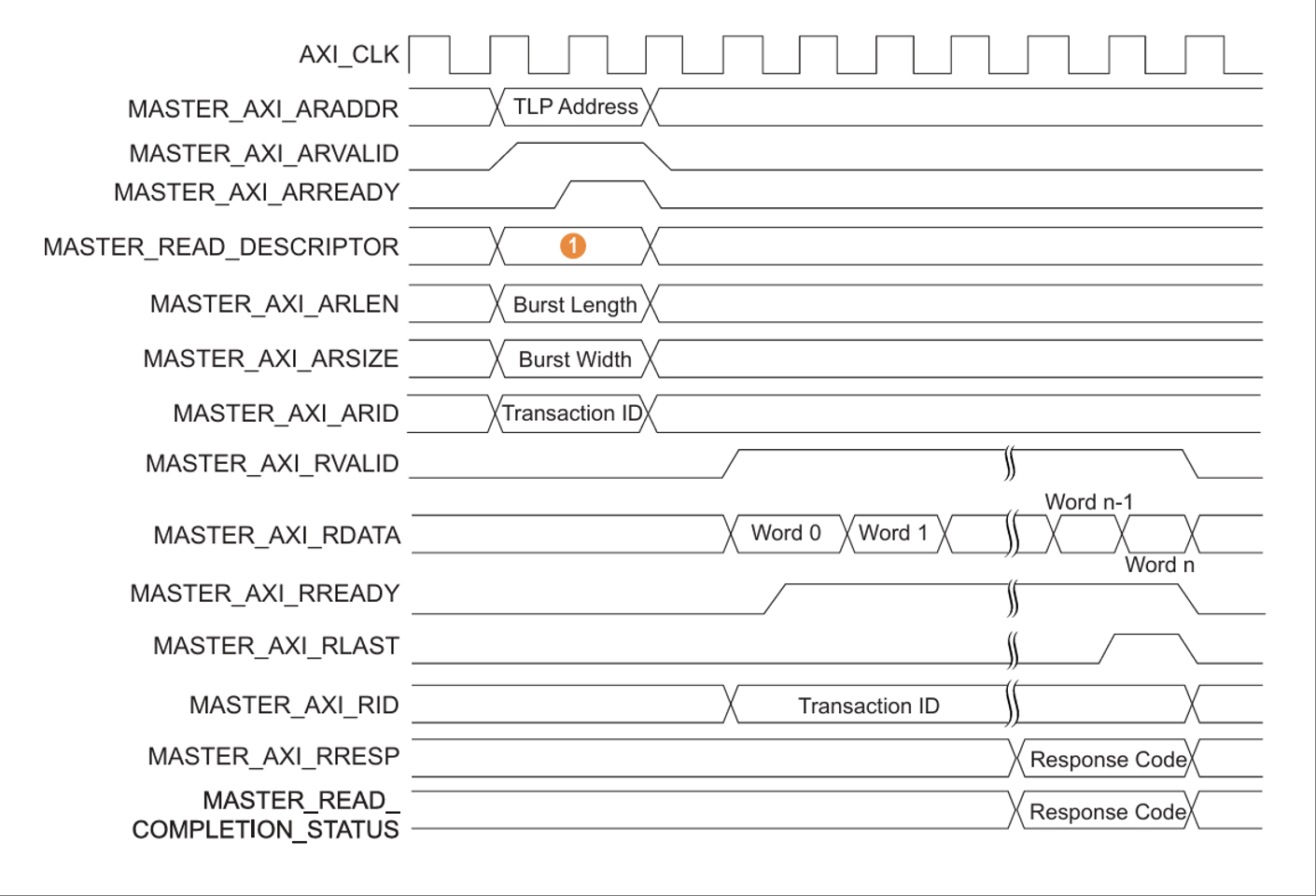

3.4.3 AXI从接口读操作:主动拉取外部数据的“自主取件”

AXI从接口读操作负责将用户逻辑发起的“外部数据读取请求”转换为Non-Posted读TLP,发送至PCIe链路(如主机内存),并将获取到的数据返回给用户逻辑。读操作是设备“主动发起、按需获取”的过程,就像自主提交“取件申请”(地址请求),等待外部响应后领取“数据包裹”,流程独立且灵活。

操作的基本流程

关键特性与特殊场景

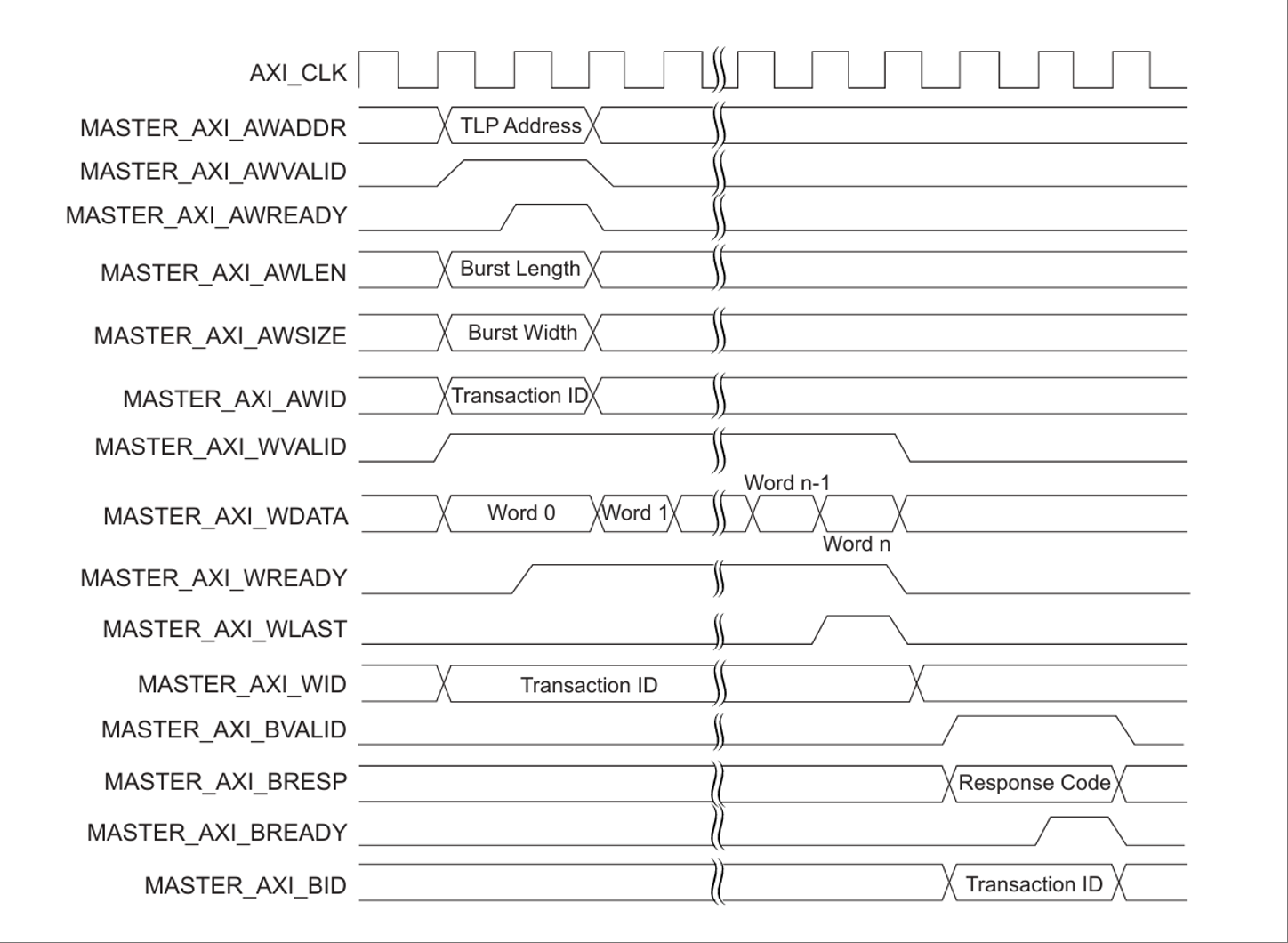

3.4.4 AXI从接口写操作:主动推送数据的“主动投递”

AXI从接口写操作负责将用户逻辑生成的数据,通过主动发起写请求的方式发送至外部(如主机内存、其他外设),核心是“设备自主发起、数据主动推送”。与主接口写操作的“被动接收、并行传输”不同,从接口写操作是设备的“主动行为”,就像主动联系“收件人”(外部设备)并完成数据投递,分为Posted(投递式)和Non-Posted(非投递式)两种类型。

操作的基本流程

关键特性与特殊场景

3.4.5 入站消息接口:PCIe消息的“专用通道”

PCIe协议中,“消息”(Message)是一种特殊TLP,用于传递控制信号(如中断、电源管理指令)。钛金PCIe控制器设计了“入站消息接口”,专门处理从PCIe链路接收的消息,相当于为消息开辟了“专用高速通道”,避免与普通数据传输冲突。

核心信号与传输规则

中断消息的特殊处理

对于中断类消息,控制器会在消息输出的同时驱动对应的中断信号(INTA_OUT至INTD_OUT),避免无效状态切换;复位时所有中断信号自动撤销,确保初始状态一致。

3.4.6 入站PCIe到AXI地址转换

PCIe设备与AXI用户逻辑使用不同的地址空间,地址转换的作用是“翻译门牌号”,确保数据能准确映射。根端口(RP)与端点(EP)的转换规则略有不同:

根端口(RP)的地址转换

端点(EP)的地址转换

3.4.7 AXI 主从接口的长度限制

PCIe和AXI协议对单次事务的长度(数据量)有明确限制,钛金控制器需遵循这些限制,避免协议违规导致的数据错误:

出站传输限制(AXI 到 PCIe)

入站传输限制(PCIe 到 AXI)

四、中断机制:设备与主机的“求救信号”

中断是设备向主机反馈状态的核心机制,相当于设备的“求救信号”-当设备发生特定事件(如数据接收完成、出现错误)时,通过中断通知主机及时处理。钛金PCIe控制器支持三种中断模式,适配不同复杂度的应用场景。

4.1 传统中断:简单场景的“基础信号”

传统中断(Legacy Interrupt)是PCI协议的经典中断模式,适配简单场景的信号反馈,核心特点是“引脚模拟”:

4.2 MSI 中断:高效简洁的“消息型信号”

MSI(Message Signaled Interrupt)是PCIe协议引入的中断模式,核心是“用内存写TLP替代引脚信号”,大幅提升中断效率和灵活性:

核心原理

MSI将中断封装为“内存写TLP”,包含目标地址(主机内存的中断处理区域)和数据(中断标识信息)。设备发起中断时,无需操作引脚,直接向主机内存发送该TLP,主机通过监测内存写入事件识别中断。

关键特性

工作流程

4.3 MSI-X 中断:多向量场景的“终极方案”

MSI-X是MSI的增强版本,针对多任务、高复杂度设备设计,核心优势是“更多向量、更灵活配置”:

核心改进

工作流程

4.4 三种中断模式的对比与选型建议

|

中断模式 |

向量数量 |

核心优势 |

适用场景 |

|

传统中断 |

最多4个(共享) |

硬件简单、兼容性好 |

低复杂度设备、传统系统 |

|

MSI |

最多32个 |

效率高、资源占用少 |

中复杂度设备、需要多个中断向量 |

|

MSI-X |

最多2048个 |

向量极多、配置灵活 |

高复杂度设备、多任务/多核心场景 |

选型核心原则:优先选择MSI-X(若设备支持),其次MSI,最后传统中断,平衡中断精准度和系统资源占用。

五、PCIe Gen4 核心技术参数对照表

|

参数类别 |

具体规格 |

备注 |

|

基础性能参数 |

单Lane速率:16Gbps(Gen4) |

相比Gen3(8Gbps)速率翻倍,核心性能提升点 |

|

最大链路宽度:x4 |

链路总带宽可达64Gbps,满足高速数据吞吐需求 |

|

|

支持100ms快速启动 |

作为EP时,可快速启动 |

|

|

支持P/N极性交换与线序交换 |

支持极性与线序灵活适配,适配复杂硬件部署场景 |

|

|

工作模式 |

支持配置:端点(EP)模式、根端口(RP)模式 |

EP作为外设接口,RP作为主控制器接口,适配不同系统拓扑 |

|

虚拟化特性 |

虚拟化支持:SR-IOV技术 |

最大4个物理函数(PF),每个PF支持16个虚拟函数(VF),总计64个VF |

|

接口特性 |

总线接口:AXI4主接口、AXI4从接口 |

主接口接收外部请求,从接口主动发起请求,兼容AMBA AXI协议 |

|

中断机制 |

支持模式:传统中断、MSI、MSI-X |

传统中断(最多4个共享向量)、MSI(32个向量)、MSI-X(2048个向量) |

|

数据保护 |

链路层:LCRC校验 |

保障TLP传输完整性,错误自动重传 |

|

端到端:字节级奇校验 |

覆盖PCIe到AXI全路径,双重数据保护 |

|

|

地址转换 |

根端口(RP):2个BAR(BAR0/BAR1)+默认BAR7 |

地址高位来自转换寄存器,低位来自PCIe地址 |

|

端点(EP):7个BAR/功能 |

每个BAR对应独立转换寄存器,适配多地址空间 |

|

|

复位与电源管理 |

复位类型:冷复位、温复位、热复位、功能级复位(FLR) |

FLR仅复位单个功能,不影响链路其他设备 |

|

电源状态:L0、L0s、L1、L1.1、L1.2、L2 |

动态调整功耗,适配高性能与低功耗场景 |

|

|

错误处理 |

高级错误报告(AER)、流量控制协议错误(FCPE) |

详细记录错误信息,支持快速故障定位 |

|

其他关键特性 |

流量优化:TPH(TLP处理提示)、Steering Tag(路由标签) |

优化缓存利用,避免传输拥堵 |

|

ACK聚合、SRIS操作 |

提升传输效率,降低硬件设计复杂度 |

综上所述,钛金PCIe Gen4高速接口方案作为国内首款适配中端FPGA的PCIe Gen4解决方案,凭借其卓越的高速低功耗特性、灵活的多协议支持以及创新的双控制器架构,为突破数据传输瓶颈提供了关键支撑。再次彰显了易灵思在FPGA领域深耕硬核技术、直击用户痛点的创新实力,持续为数字经济发展注入高速、灵活与高效的连接动力。