技术新闻 09-04

微处理器传统上一直主导着计算领域,在需求更多算力的推动下,硅基器件在密度方面不断得到提升。按照摩尔定律,每隔两年,晶体管密度就会翻番,这无疑是技术创新的金矿。在这场“淘金热”中,考虑到定制硅涉及的专业知识和费用,几家大型半导体公司已在市场上斩获了稳固地位。现在,随着对计算密集型器件需求的不断增长,ASIC、FPGA和嵌入式处理器等都被要求执行更复杂的任务。而进入的壁垒一直高得令人望而兴叹。

在整个产业链的终端应用方面,系统的实施在很大程度上取决于利润。IC的开发成本、专利许可费和设计的便捷性都直接影响了创建现代电子产品的价格。设计师和开发者一般都依赖硬件加速电路与传统的嵌入式处理器来完成 和专用标准产品(ASSP)中的核心功能,同时通用处理器众所周知的设计流程也提供了诸多便捷与可靠性。其根本目标是:以最低成本实现快速上市,同时满足现代应用日益增长的复杂计算需求。那么问题就变成了:哪种(些)芯片组合能够以最少的开发时间和成本,而最有效地实现这些应用?

这正是易灵思FPGA一显身手的地方。易灵思FPGA借助简单的软件方法进行软硬件分工,将FPGA的固有架构优势与流行的嵌入式处理器的便捷编程特性相结合。本文将介绍这种充分发挥FPGA潜力的新设计方法,如何使设计师能最大限度地提高系统设计能力和效率。

易灵思钛金系列FPGA在低端和高端FPGA之间取得平衡,是款兼具高密度、小封装、低功耗和低价格等优势的器件。通过16nm工艺技术,钛金系列FPGA可以在小至5.5 × 5.5mm的封装中集成了多达100万个逻辑单元(LE)、以及大量存储模块和高速DSP模块。

这是由于易灵思的Quantum®计算内核具有可重新配置的模块,即逻辑和路由可互换的XLR单元。这消除了传统布线,让LE更小、使用更灵活,与传统FPGA相比,利用率非常高。当需要时,软RISC-V核可在FPGA内核中被例化。在编译时,易灵思的软件会动态选择是将XLR单元用作路由还是逻辑功能,以优化其芯片资源。并且,易灵思FPGA实现的RISC-V CPU架构,不受ARM等专IP内核的约束,规避了任何专利许可费用。

RISC-V是一种免费的指令集架构(ISA),它附带多种软件参考设计、IP软核和实体器件。RISC-V和ARM之间的主要区别在于:RISC-V是一个开放标准,其中ISA没有定义任何特定的微处理器架构;其它流行的处理器技术(如:x86、x64 和ARM)都是基于使用供应商提供的ISA和硬件架构而付费的商业模式。

模块化、开源RISC-V架构的日益普及,使开发者可以免版税使用这些内核并创建非指定供应商的计算方案。随着摩尔定律继续放缓,这为创新打开了大门。RISC-V处理核可以集成到FPGA中,以将便捷编程特性,与FPGA和ASIC架构的并行处理能力和灵活性/可重配置性相结合。

易灵思FPGA的优点并不仅限于其优化的成本和性能。”量子加速”概念还带来了与传统嵌入式处理器相同的编程便捷性。量子加速依赖于两种关键技术来简化和优化设计流程与设计本身:

1、使用RISC-V处理器

2、使用量子加速器

首先,高度可扩展的RISC-V处理器被用作系统主力,以确保系统功能最大程度的在软件中表达。使用RISC-V处理器的一个固有优势是其自定义指令,可用于扩展处理器的功能以满足应用要求。这确保在使用熟悉的C/C++语言的同时,以最高效率由处理器在本地执行高度加速的任务。

因此,若要用C语言对没有自定义扩展指令的的传统嵌入式处理器编写卷积任务程序,设计师必须将其分解为几条更简单的指令。而使用RISC-V自定义指令,则可以在一次执行中完成上述任务。这些基于特定应用的指令大大减少了标准指令所需的周期数,并通过降低功耗大大提高了系统效率。对于人工智能算法中通常使用的卷积,使用自定义指令可将卷积加速40至50倍。从而显著提高了系统性能。

定制指令还能让更广泛的产品组合,更快的上市。易灵思的一个合作伙伴创建了一个包含数百个自定义指令的库,这些指令可被例化并按需调用。这给他们带来的效果是:可以在一个通用的硬件平台上,定义、创建和快速交付众多的用户产品,而产品间的差异仅靠RISC-V处理器的软件优化就可实现。

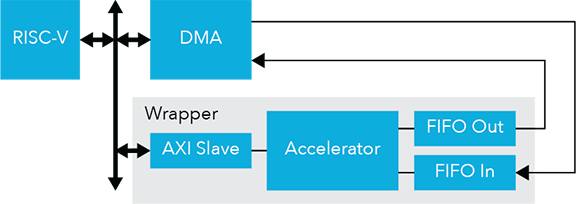

然而,自定义指令往往适合较少量的数据处理。如果用户希望对更大数据块执行数学函数运算。量子加速器套接字(socket)定义了一个框架,使用户能够根据应用的要求轻松地“指向”数据、检索数据并编辑其内容。此加速器套接字具有针对加速器功能、RISC-V处理器、直接内存访问(DMA)控制器和其它处理模块的特定输入和输出(见图)。DMA、回调(callback)和与RISC-V处理器的连接都在 C中调用,并几乎替程序员自动执行。所需要的只是一点用于加速的VHDL代码,而易灵思也已经提供了许多相关示例。

图1

说明:易灵思量子加速器套接字具有特定的输入和输出,使用户能够指向大数据块对其检索和编辑并进行硬件加速。该套接字只需最小的VHDL设计就可以无缝地进行后续数据移动,因此设计师可以简单地只需紧盯性能瓶颈就好。

这种方法的好处体现在极大地缩短了上市时间。使用这种预定义的加速建构,易灵思的一位合作伙伴设计了一款相机系统,包含输入传感器、人工智能引擎、目标检测和分类、以及输出显示子系统。从项目启动到功能齐全的样机以及量产,整个过程才耗时一周多一点。

总之,易灵思FPGA既利用了开放式RISC-V标准的固有优势,又结合了使用定制指令或能快速修改大块数据的定制加速器框架的长处。这使电子设计公司和制造商能够实现以下目标:

易灵思把FPGA从传统的不起眼的设计替代品转变为设计必需品。这些设计技术模糊了传统系统架构的界限。随着可配置、经济、低功耗、具传统嵌入式处理器方案速度的FPGA的推出,借助以下方式可推动大众市场采用这些平台:

在保有传统嵌入式处理器(例如ARM)设计流程简单性的情况下替换嵌入式处理器

与ASIC等定制芯片相比,构思和生成基于FPGA的方案所需的时间已大为缩短。在成品足够便宜时,在适应性强的FPGA上实现定制功能,是可以取代ASSP。易灵思嵌入式RISC-V处理器也可以进行定制,以模仿和扩展现有MCU的功能。从模仿一款熟悉的MCU开始,可以在FPGA架构中例化增强的自定义功能以及自定义加速模块和 I/O信号调整。

最重要的范式转变在于能够利用传统嵌入式处理器(例如ARM)设计流程的简单性进行快速创新。高度集成的 易灵思方案包含了已为人熟知的控制器架构和高度加速的配套模块的各种衍生品,所有这些都在同一个硅芯片中。这为易灵思FPGA在边缘计算之外——从基本的物联网设备到数据中心卡——的更多样化市场打开了大门。

对于很多以往需要用到通用嵌入式处理器+强大的FPGA的设计,设计师们现在可以用更简单的方式在FPGA上实现。传统上利用标准CPU或MCU(例如物联网传感器节点)的项目现在都可以被FPGA所取代,且功耗相当(如果不是更少的话),外形小巧、成本低廉以及可以直接采用软件设计流程。还有最大的好处是:基于易灵思FPGA平台的架构灵活性,这些设计自来就是面向未来且可升级的。

推动器件向高算力迈进的设计师也可以借力易灵思FPGA。这使业务能够从传统的物联网和宽带用例(如家庭自动化、机器监控和移动设备上的常用高清视频流)转向下一代应用,如自动驾驶汽车、无缝沉浸式现实体验(AR/VR头戴设备)等等。易灵思FPGA还可以满足这些基于边缘、高带宽或时间敏感的用例。企业可以通过正确的处理能力来满足未来计算要求,从而有效地训练、运行和升级各自的机器学习算法。

易灵思FPGA可以显著简化设计周期,立即摆脱对ASIC的硬件开发要求,并简化相对CPU和GPU不够直接的硬件加速过程。这种FPGA产生了巨大影响,将FPGA带入了很多以往不可企及的新市场。在向熟悉的软件技术开放硬件设计环境的过程中,易灵思极大扩展了可移植到FPGA的设计范围,进一步缩短了上市时间并提高了最终用户应用的灵活性。由此带来的成本和密度优势将使FPGA在市场上的拓展远远超出传统的应用范畴,并推动其进入可触及我们生活方方面面的应用。